Transmitter pll bandwidth setting – Altera Stratix GX Transceiver User Manual

Page 25

Altera Corporation

2–7

January 2005

Stratix GX Transceiver User Guide

Stratix GX Analog Description

If the reference clock exceeds 325 MHz, the clock must be fed by the

dedicated local reference clock pin, REFCLKB. By default, the Quartus II

software assigns pins to be LVTTL, so you must assign the 1.5-V PCML

I/O standard to the I/O pins to select the REFCLKB port as the reference

source. The Quartus II software prompts a fitter error if the reference

clock exceeds 325 MHz and the reference clock source is not on the

REFCLKB

port.

You can also use the pre-divider on the REFCLKB path to support

additional multiplication factors. The block diagram in

that /m can only support multiplication factors of 4, 8, 10, 16, and 20, but

shows that the additional multiplication factors of 2 and 5 are

also achievable. You can achieve these multiplication factors by using the

pre-divider. A multiplication factor of 2 is achieved by pre-dividing the

reference clock by 2 and then multiplying the resultant frequency by 4,

which yields a multiplication factor of 2. A multiplication factor of 5 is

achieved in the same manner by pre-dividing the reference clock by 2 and

then multiplying the resultant frequency by 10, which yields a

multiplication factor of 5.

lists the possible multiplication values as a function of the

source to the transmitter PLL.

assumes that the reference clock

is directly fed from the source listed and does not factor any pre-clock

synthesis (that is, the Stratix GX PLL driving a global clock that is used for

the transmitter PLL reference clock source).

You must specify the data rate of the channel and input clock period of

the reference clock. The data rate divided by the input clock period must

equal one of the multiplication factors listed in

Transmitter PLL Bandwidth Setting

The Stratix GX transmitter PLL in the transceiver block offers a

programmable bandwidth setting. The PLL bandwidth is the measure of

its ability to track the input clock and jitter. The bandwidth is determined

by the –3-dB frequency of the closed-loop gain of the PLL.

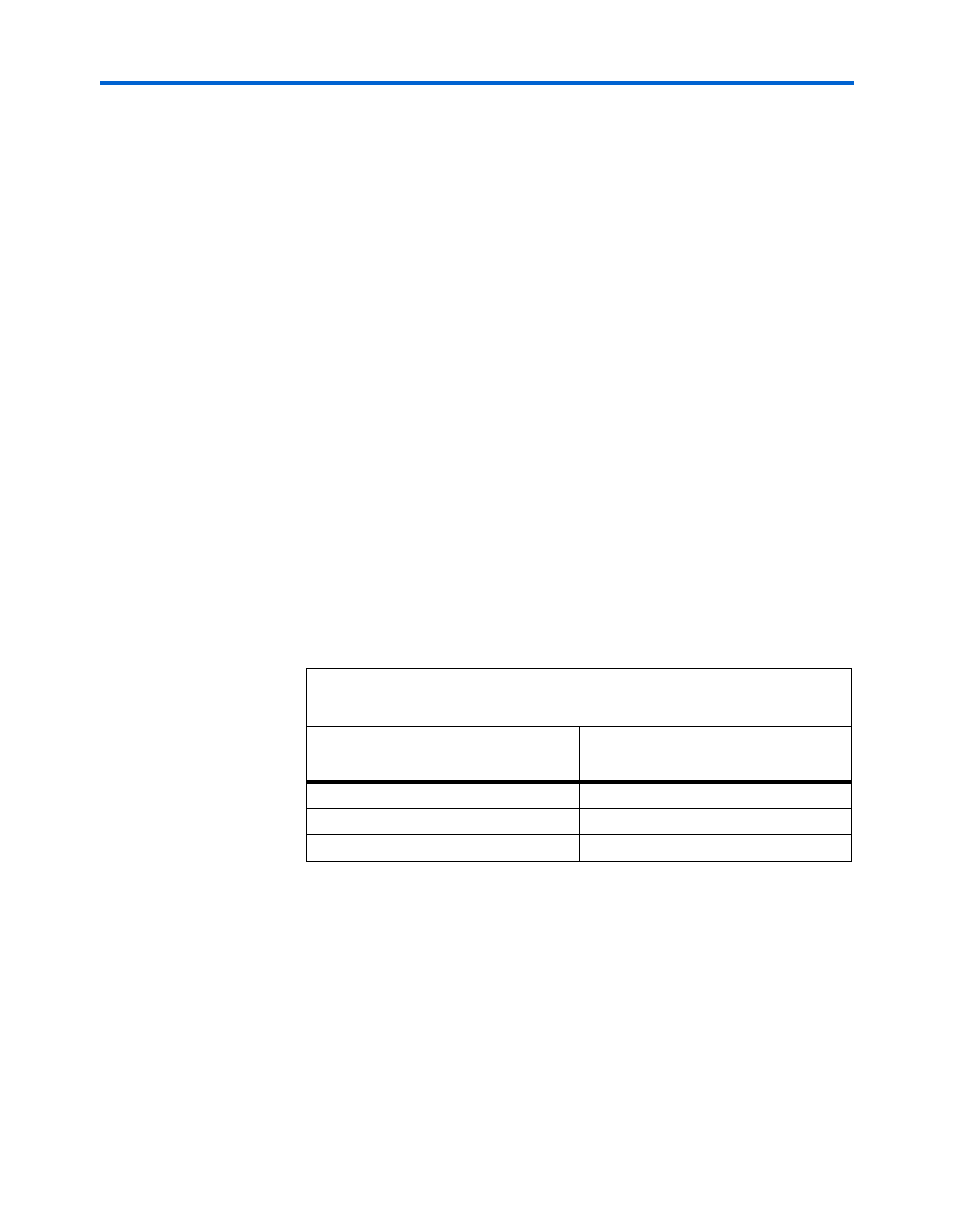

Table 2–3. Multiplication Values as a Function of the Reference Clock

Source to the Transmitter PLL

Transmitter PLL Reference Clock

Source

Multiplication Factors

Global clock, I/O bus, general routing

4, 8, 10, 16, 20

Inter-transceiver routing

2, 4, 5, 8, 10, 16, 20

Dedicated local REFCLKB

2, 4, 5, 8, 10, 16, 20