Top-level design (incremental), Figure 8–5, Shows – Altera Stratix GX Transceiver User Manual

Page 216

8–12

Altera Corporation

Stratix GX Transceiver User Guide

January 2005

Design Examples

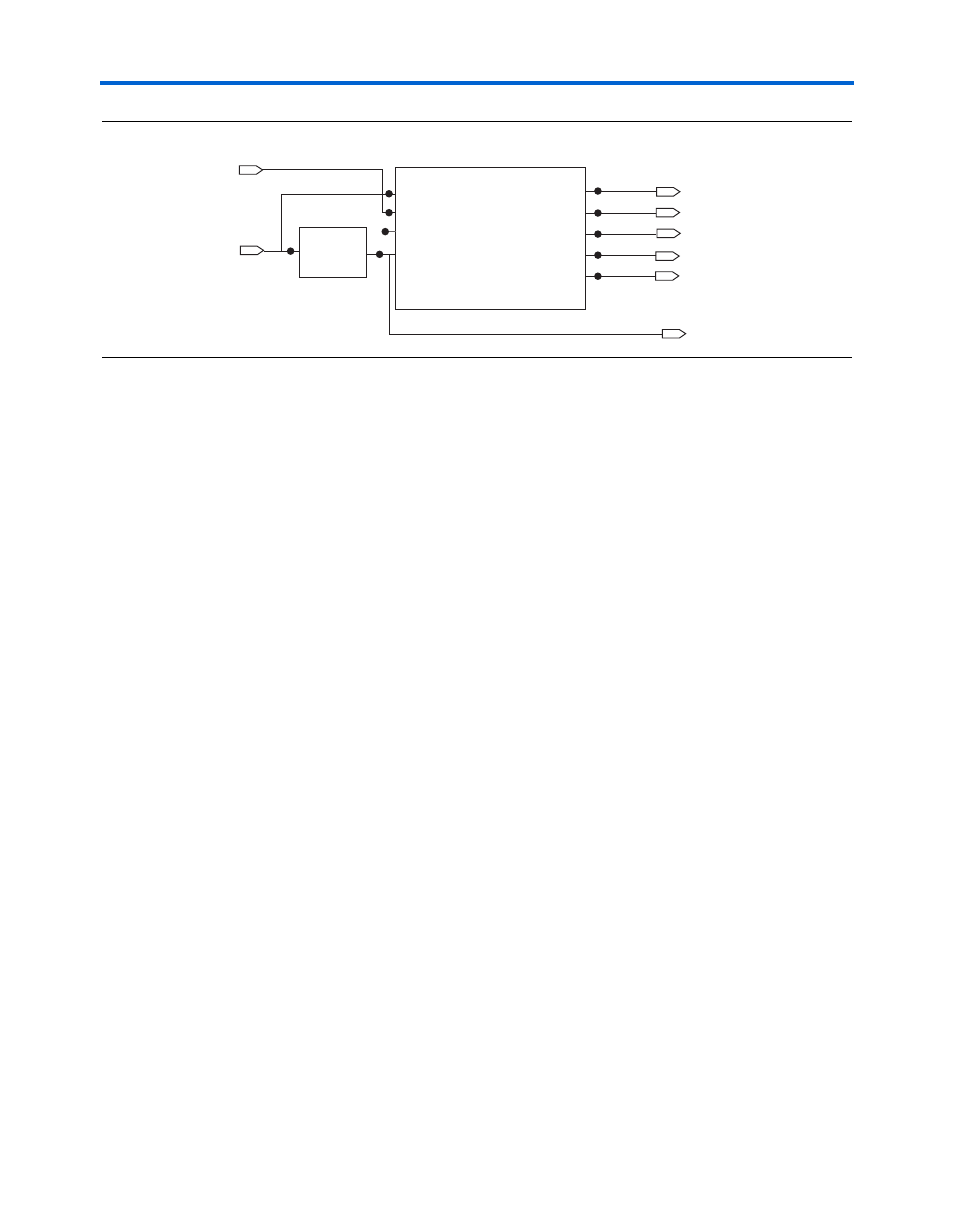

Figure 8–5. Block Diagram of the Incremental BIST Design

Top-Level Design (Incremental)

module incremental(

inclk,

rx_in,

coreclk_out,

tx_out,

rx_bisterr,

rx_bistdone,

rx_clkout,

reset

);

input

inclk;

input

rx_in;

outputcoreclk_out;

output tx_out;

outputrx_bisterr;

output rx_bistdone;

output rx_clkout;

output reset;

wire

reset_wire;

wire

VCC;

assign reset = reset_wire;

assign VCC = 1;

Incr_BIST Incr_BIST_inst(

.inclk(inclk),

.rx_in(rx_in),

.rx_slpbk(VCC),

.rxdigitalreset(reset_wire),

inclk

rx_in

tx_out

coreclk_out

rx_clkout

rx_bistdone

rx_bisterr

Incr_BIST

tx_out[0]

coreclk_out[0]

rx_clkout[0]

rx_bistdone[0]

rx_bisterr[0]

reset

Incr_BIST_inst

inclk[0]

rx_in[0]

rx_slpbk[0]

rxdi

g

italreset[0]

reset_mod

clk

reset

reset_mod_inst