Altera Stratix GX Transceiver User Manual

Page 67

Altera Corporation

3–21

January 2005

Stratix GX Transceiver User Guide

Basic Mode

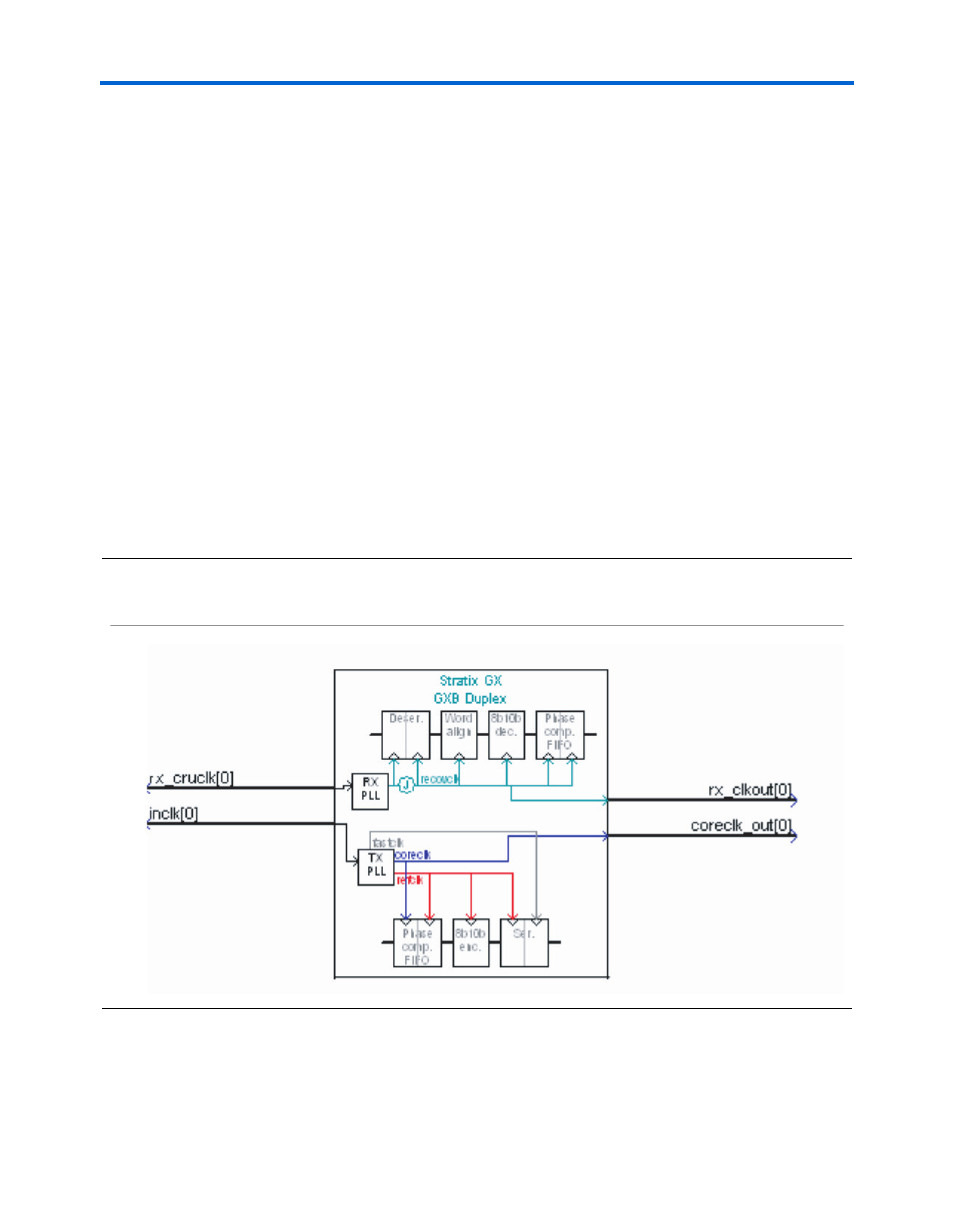

On the transmitter channel the output of the transmitter PLL,

coreclk_out

, is sent into the logic array and also loops back to clock the

write side of the transmit phase compensation FIFO buffer.

You can disable the trained receiver PLL CRU clock from the transmitter

PLL feature in the MegaWizard Plug-In Manager. Deselecting this option

adds an additional RX_CRUCLK input reference clock port for the receiver

PLL. This feature supports additional multiplication factors for the

receiver PLL and also supports the separation of receiver and transmitter

reference clocks. This separation is required if the output reference clock

frequency from the transmitter PLL exceeds the 325-MHz phase

frequency detector of the receiver PLL. For more information on this

feature, refer to the Stratix GX Analog Description chapter. This

configuration is shown in

.

If double width is used (16-bit bus) and the data rate is above 2,600 Mbps,

the train receiver PLL clock from the transmitter PLL must be turned off,

because the output clock from the transmitter PLL exceeds the 325-MHz

limit on the receiver PLL input clock, if the input clock is fed by any

non-REFCLKB pins. REFCLKB input pins have a 650-MHz limit.

Figure 3–20. altgxb Megafunction in Basic Mode With the Train Receiver CRU From Transmitter PLL

Disabled