Serializer (parallel-to-serial converter) – Altera Stratix GX Transceiver User Manual

Page 26

2–8

Altera Corporation

Stratix GX Transceiver User Guide

January 2005

Transmitter Analog

A high-bandwidth setting provides a faster lock time and tracks more

jitter on the input clock source which passes it through the PLL. This

helps reject noise from the VCO and power supplies. A low-bandwidth

setting, on the other hand, filters out more high frequency input clock

jitter, but increases lock time.

You can set the bandwidth for Stratix GX devices to either low or high.

The –3-dB frequencies for these settings can vary due to the non-linear

nature and frequency dependencies of the circuit. As a result, you can

vary the bandwidth to customize the performance on specific systems.

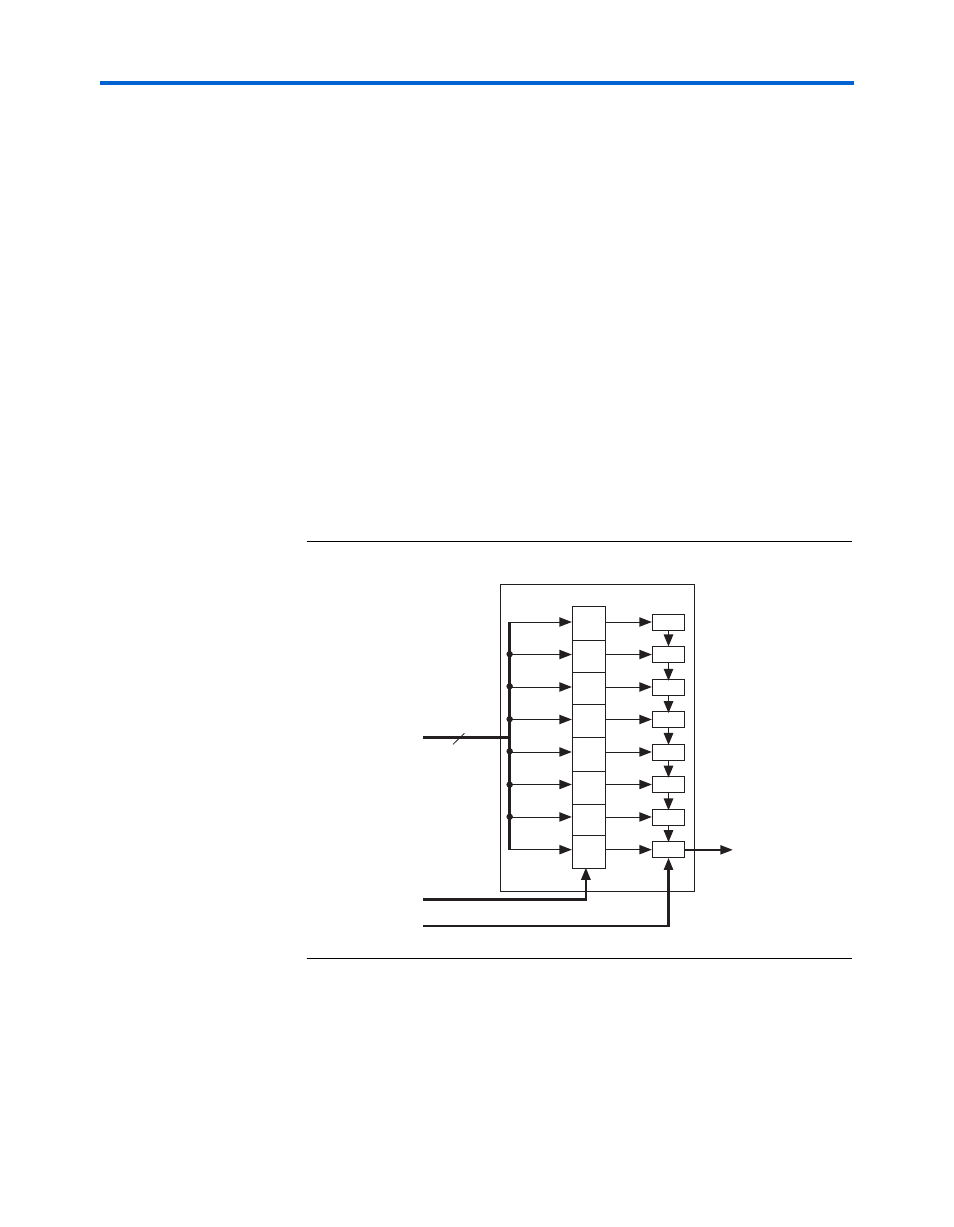

Serializer (Parallel-to-Serial Converter)

The serializer converts parallel data to serial data at the transmitter

output buffer. The serializer can support 8- or 10-bit words when used

with the transmitter multiplexer. The 8-bit serializer drives the serial data

to the output buffer, as shown in

. The serializer can drive the

serial bit-stream at a data rate range of 500 Mbps to 3.1875 Gbps. The

serializer outputs the least significant bit (LSB) of the word first.

Figure 2–5. Example of 8-Bit Serialization

shows the serial bit order of the serializer output. In this

example, a constant 8’h6a (01010110) value is serialized.

1

The serial data is transmitted from LSB to most significant bit

(MSB).

D7

D8

D6

D3

D4

D2

D1

D0

D7

D8

D6

D3

D4

D2

D1

D0

Low-Speed

Parallel Clock

High-Speed

Serial Clock

Parallel Data

8

Serial Data Out

(I/O Output Buffer)

Serializer