Altera Stratix GX Transceiver User Manual

Page 72

3–26

Altera Corporation

Stratix GX Transceiver User Guide

January 2005

Basic Mode Clocking

Another inter-transceiver block consideration is the selection of the

dedicated REFCLKB pin. Stratix GX channels are arranged in banks of

four, or transceiver blocks. Each transceiver block is able to share a

common reference clock through the inter-transceiver lines. You can

reduce the Stratix GX logic array clock usage by using the inter-

transceiver lines. The inter-transceiver lines are used when a REFCLKB

input port from one transceiver block or channel drives any other

transceiver blocks or channels. The Quartus II software automatically

determines the inter-transceiver line usage.

When determining the location of REFCLKB pins, you should consider

what is fed by the chosen pin.

shows the available

inter-transceiver lines, along with the transceiver block that drives them.

This information is based on the number of transceiver channels in the

Stratix GX device.

shows the transceiver routing with respect to inter-

transceiver lines for the EP1SGX25 device. It is important to use this

information when placing REFCLKB pins. For example, if a REFCLKB pin

is used and is required to feed a transmitter PLL using an inter-

transceiver line, the REFCLKB pin cannot be in transceiver block 1,

because IQ2 feeds only the receiver PLLs.

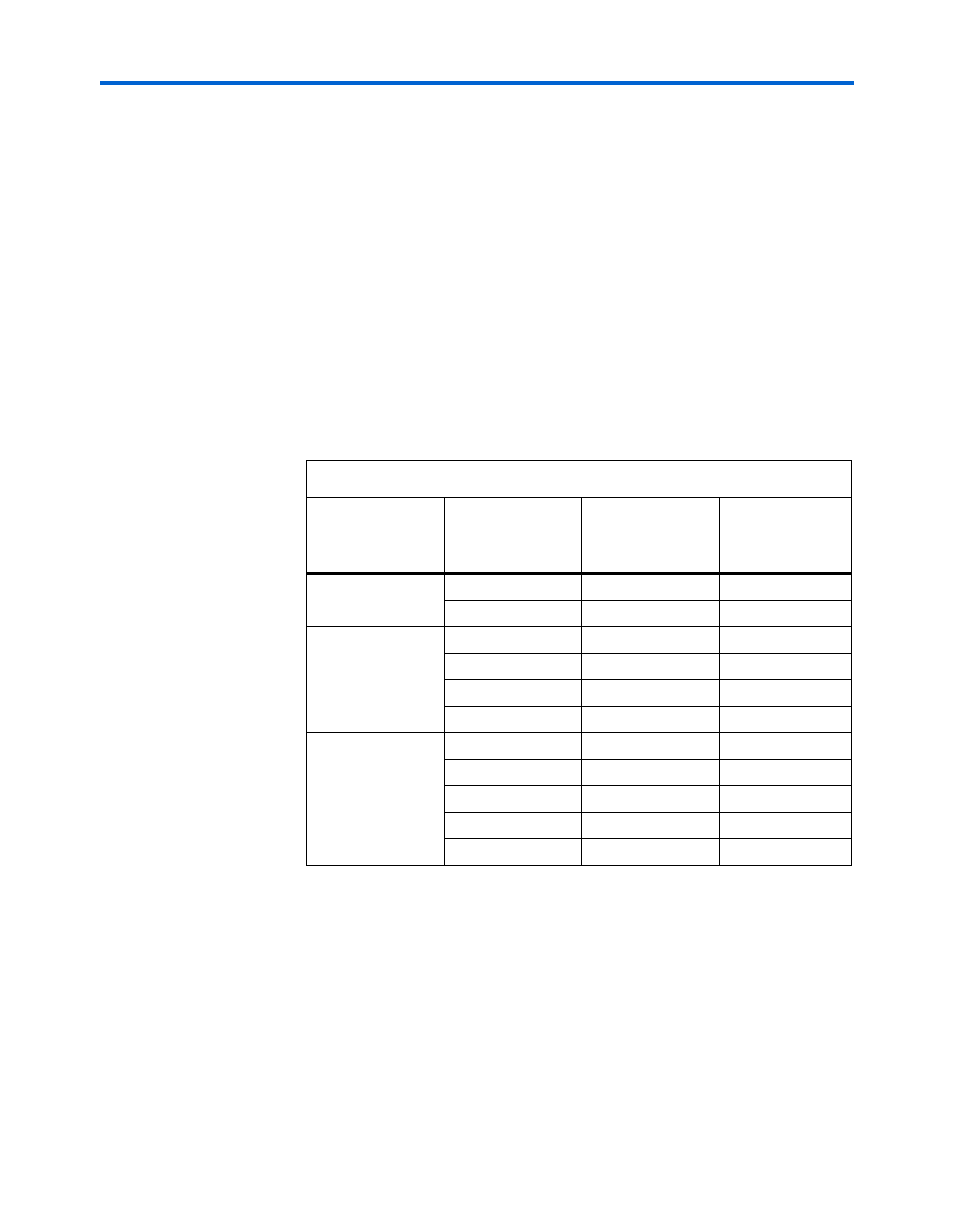

Table 3–4. REFCLKB to IQ Line Connections

Channel Density

REFCLKB in

Transceiver Block

Number

Channels in

Transceiver Block

IQ Line Driven by

REFCLKB

8 channels

(EP1SGX10)

0

[3:0]

IQ2

1

[7:4]

IQ0

16 channels

(EP1SGX25)

0

[3:0]

N/A

1

[7:4]

IQ2

2

[11:8]

IQ0

3

[15:12]

IQ1

20 channels

(EP1SGX40)

0

[3:0]

N/A

1

[7:4]

IQ2

2

[11:8]

IQ0

3

[15:12]

IQ1

4

[19:16

N/A