Receiver reset – Altera Stratix GX Transceiver User Manual

Page 258

9–32

Altera Corporation

Stratix GX Transceiver User Guide

January 2005

Recommended Resets

Receiver Reset

The configurations and design examples in this section describe how to

implement a reset sequence for the receiver channels. This section

describes the reset sequence only. Each design example lists the

constraints specific to the example to help you understand the design

parameters and limitations. You may want to add additional escape states

and other system-specific features in your design. If your design

requirements are different from the design example, you can make

necessary changes using the flow chart and waveform figures in each

section as guidelines.

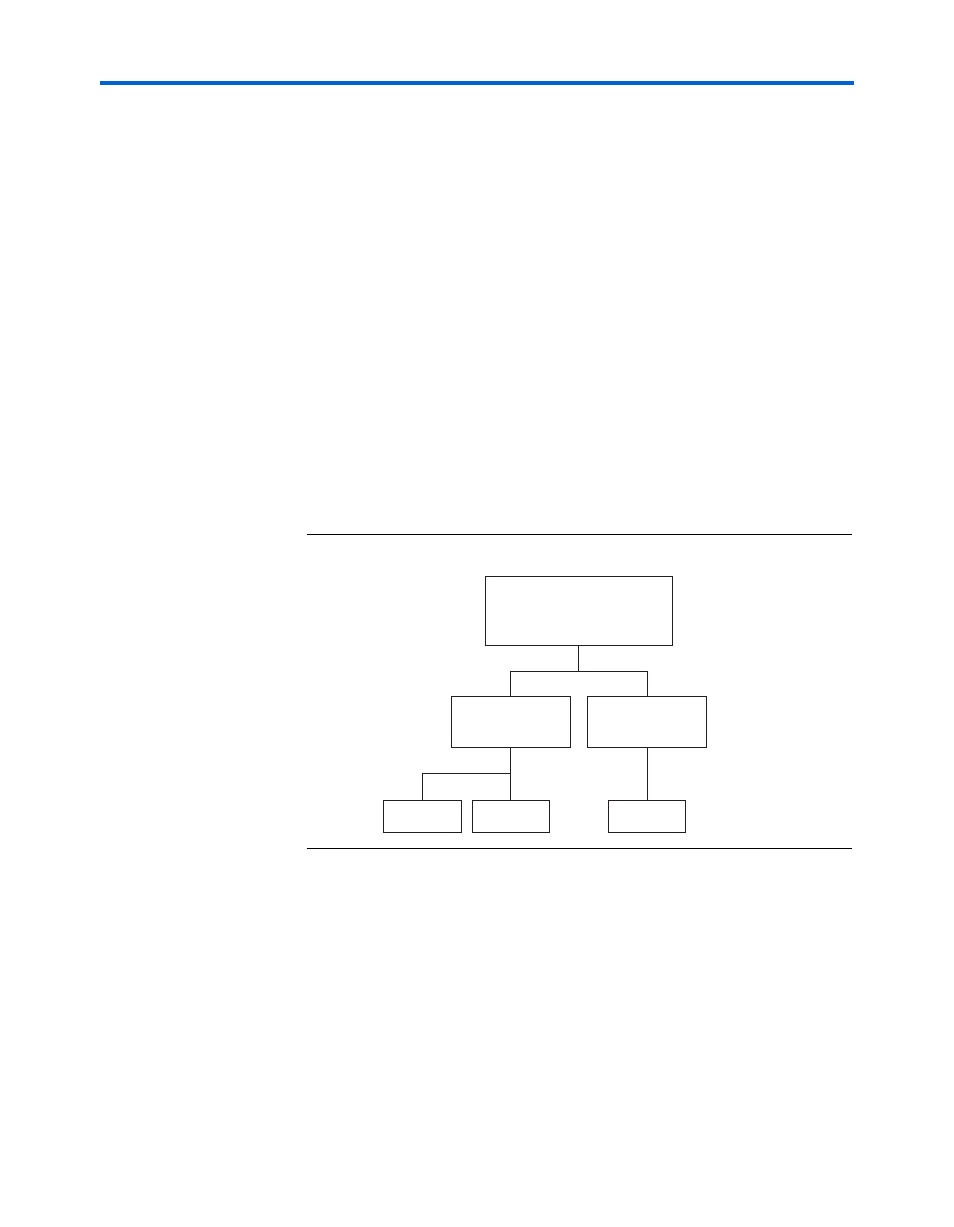

Receive CRU With Transmit PLL Output Clock Option Enabled

This section provides some design examples that show a receive-only

configuration with train receive CRU and the transmit PLL output clock

enabled.

shows the receive-only clock options.

Figure 9–10. Receiver Only With Clock Options Enabled

The flow chart in

shows a situation where only the receive

channel requires a reset sequence.

Receive Only with Train RX

CRU with TXPLL output clock

option enabled

Single Width

(8/10)

Double Width

(16/20)

rx_clkout

rx_coreclk

rx_clkout

Receive Parallel Clock

data path width

Receive Parallel Clock