Figures 2–13 – Altera Stratix GX Transceiver User Manual

Page 39

Altera Corporation

2–21

January 2005

Stratix GX Transceiver User Guide

Stratix GX Analog Description

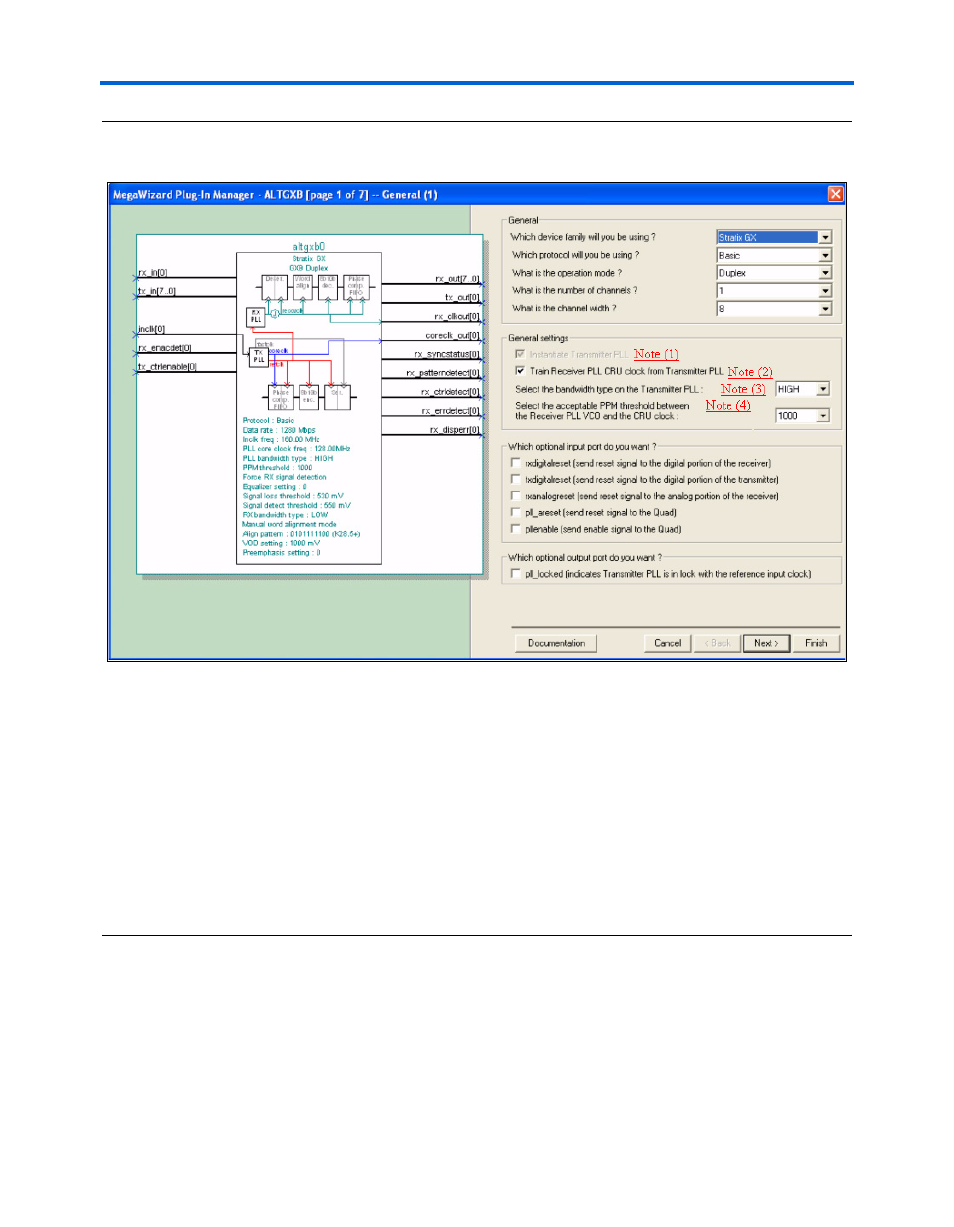

Figure 2–13. MegaWizard Plug-In Manager - ALTGXB (Page 1 of 7) - General (1)

–

Notes to

:

(1)

Option available in receiver-only mode: Supports use of the transmitter PLL even when the transmit channel is disabled.

Provides a non-recovered clock output for the logic array.

(2)

Enables the transmitter PLL to train the receiver PLL: Use this option to support additional multiplication factors for

the receiver PLL. This option also supports the separation of receiver and transmitter reference clocks. An additional

input receiver reference clock (

rx_cruclk

) is available when this option is turned off. The first option that is

enabled is needed for non-encoded 16-bit modes with a line rate of 2,600 Mbps or greater. For more details regarding

this feature, refer to

.

(3)

Selectable High and Low: High bandwidth supports faster lock times. It also tracks higher frequency jitter (based on

the –3-db frequency of the PLL gain plot) on the input clock. Low bandwidth has a smaller pass band to filter out

more high-frequency jitter, but has a slower lock time.

(4)

Selectable PPM difference tolerance {125, 250, 500, 1000} between the Receiver PLL VCO and the CRU clock: This is one of

three parameters that affect the rx_freqlocked signal. If an out-of-tolerance event occurs, rx_freqlocked goes

low.