Stratix gx built-in self test (bist), Introduction, Chapter 8. stratix gx built-in self test (bist) – Altera Stratix GX Transceiver User Manual

Page 205: Introduction –1

Altera Corporation

8–1

January 2005

8. Stratix GX Built-In Self Test

(BIST)

Introduction

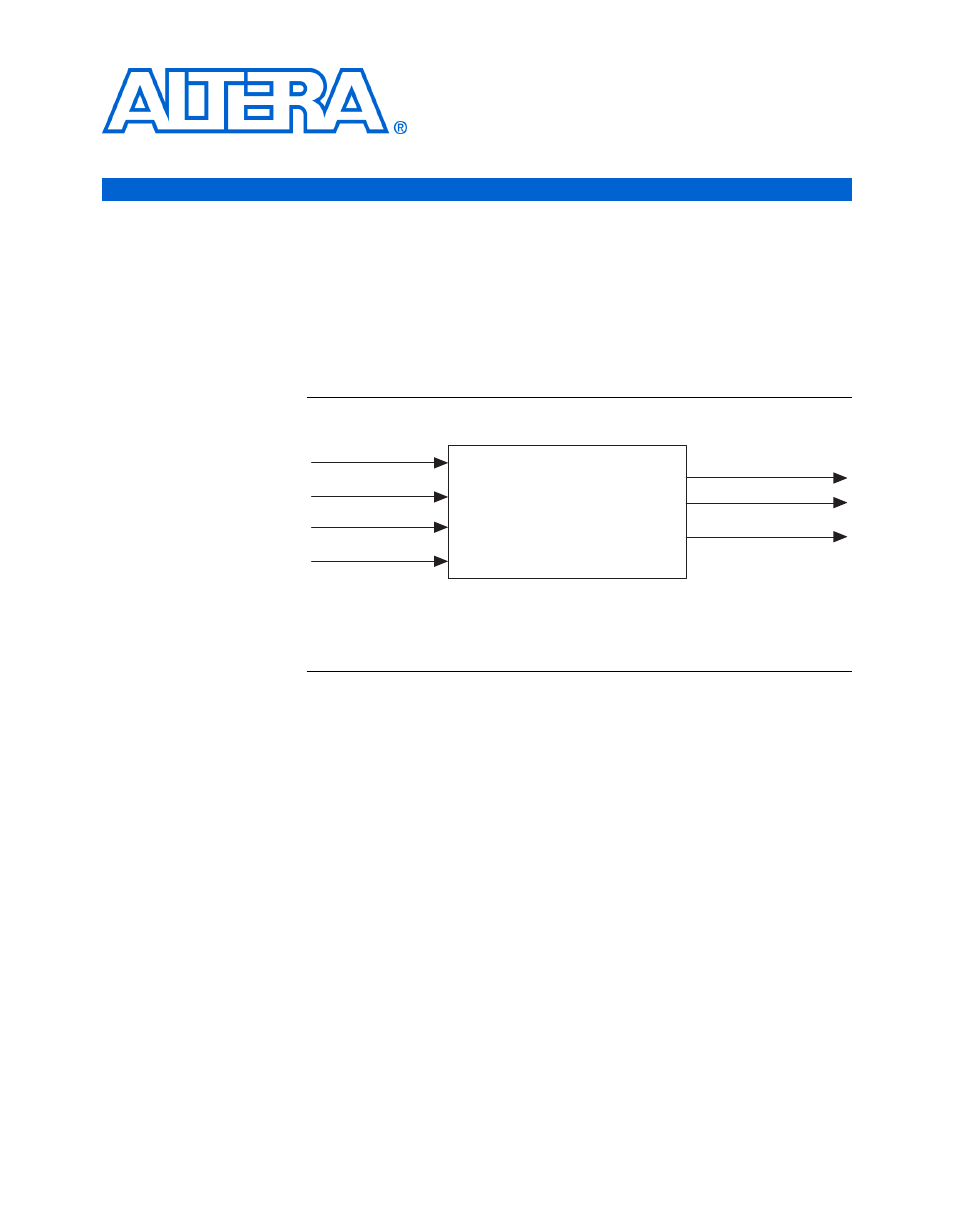

Each Stratix

®

GX channel in the gigabit transceiver block contains

embedded built-in self test (BIST) circuitry, which is available for quick

device verification. The BIST circuitry consists of a data generator that

resides in the transmitter channel and a verifier that resides in the receiver

channel.

shows a simplified block diagram of the BIST

circuitry.

Figure 8–1. Image of Stratix GX Built-In Self Test

Notes to

:

(1)

rx_slpbk[]

is required in PRBS and incremental BIST modes.

(2)

rx_bisterr[]

and rx_bistdone[] are only available in PRBS and incremental

BIST modes.

The BIST data generator is configured to generate pseudo-random binary

sequence (PRBS), incremental, high-frequency, low-frequency, or mixed-

frequency patterns. The BIST verifier supports only the PRBS and

Incremental modes. The remaining BIST modes are intended for quick

evaluations of the transmitters. The Quartus

®

II software simulation

models do not support the PRBS patterns generated in the BIST circuit.

shows the BIST modes.

Built-In Self Test

(BIST)

txdigitalreset[]

rxdigitalreset[]

rx_bisterr[]2

rx_bistdone[]2

tx_out[]

rx_slpbk[]1

inclk[]