Figure 5–22 – Altera Stratix GX Transceiver User Manual

Page 138

5–26

Altera Corporation

Stratix GX Transceiver User Guide

January 2005

XAUI Mode Clocking

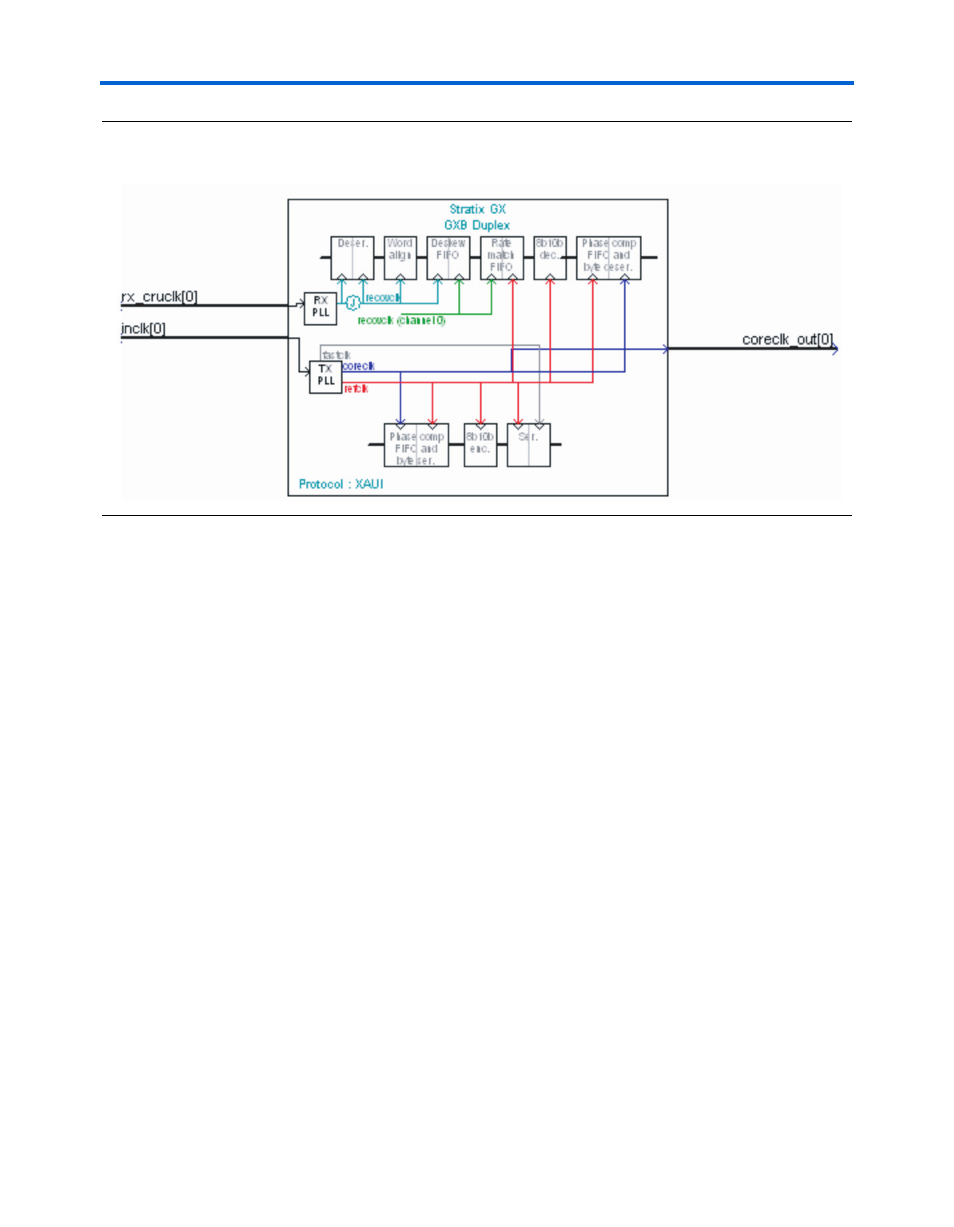

Figure 5–22. Train Receiver PLL CRU Clock From Transmitter PLL Feature Is Disabled With Added Port

RX_CRUCLK

If tx_coreclk is enabled, the train receiver CRU clock from transmitter

PLL is disabled, and if other default options are also enabled, this

configuration has an independent rx_cruclk that feeds the receiver

PLL reference clock. This input clock port is only available when the

receiver PLL is not trained by the transmitter PLL.

You can enable the write clock of the transmitter phase compensation

FIFO module to manually feed in a clock from the FPGA logic array. You

can use this option to optimize the global clock usage. For instance, if all

transmitter channels between transceiver blocks are from a common

clock domain, the transceiver instantiations use a total of one global

resource instead of one global per transceiver block if the tx_coreclk

option is not enabled. On the transmitter functionality screen under the

optional port of transmitter section, if tx_coreclk is selected as an input

port, the default clocking scheme changes by using tx_coreclk as the

write clock for the phase compensation FIFO module.

There are two ways to connect tx_coreclk. To use coreclk_out,

connect coreclk_out to tx_coreclk by using either

gclk

/rclk/fclk or logic array routing. Alternatively, tx_coreclk

can be supplied from a crystal or any other clock source, as long as

tx_coreclk

is frequency-locked to the read side of the phase

compensation FIFO module on the transmit side.