Figure 4–11 – Altera Stratix GX Transceiver User Manual

Page 95

Altera Corporation

4–13

January 2005

Stratix GX Transceiver User Guide

SONET Mode

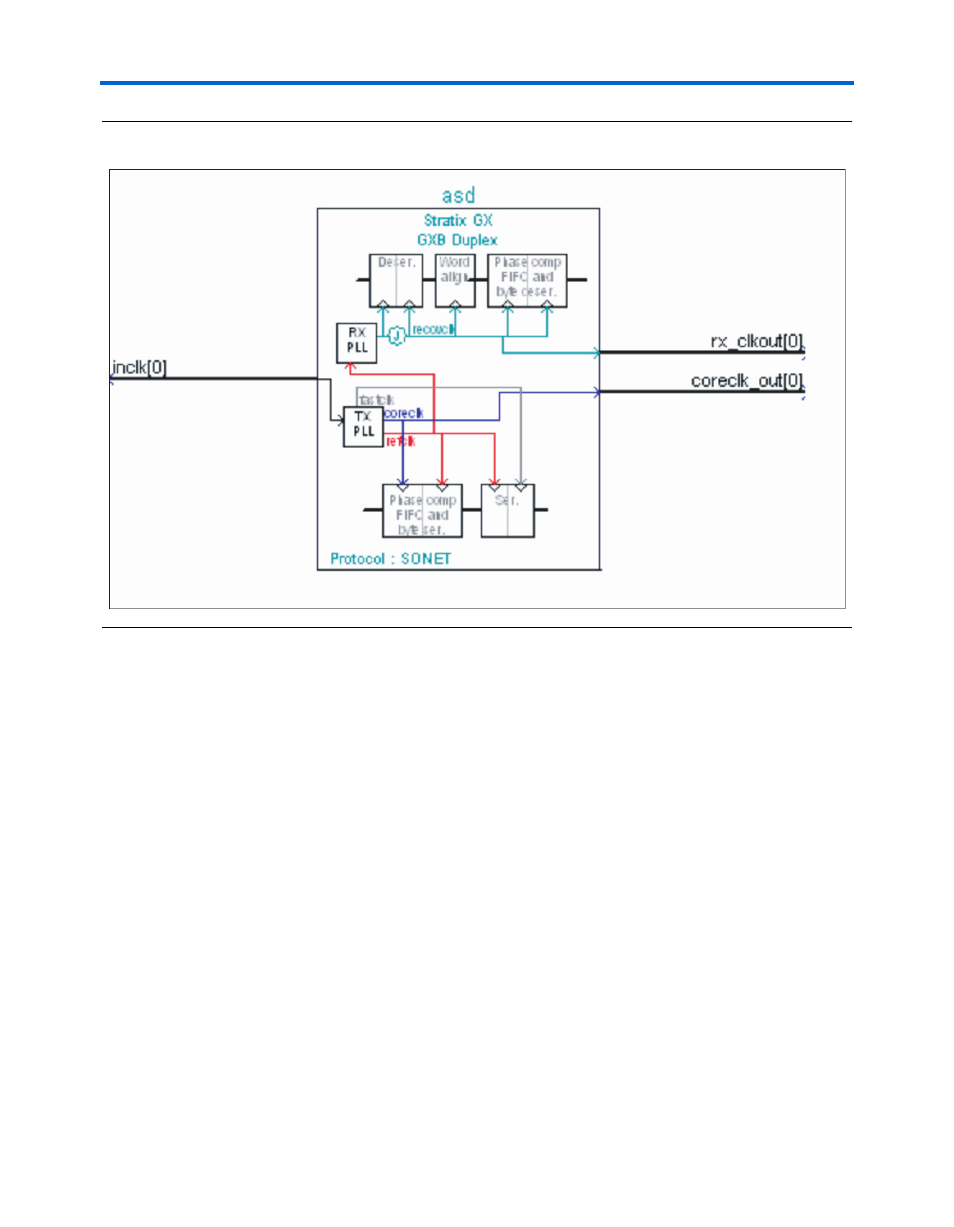

Figure 4–11. Default Configuration of altgxb in SONET Mode

In

, the altgxb megafunction is configured so that the train

receiver PLL with transmitter PLL is enabled. The transmitter PLL is fed

from an inclk port, which can be fed from a dedicated REFCLKB, Global

clock, Regional clock, or Fast Regional clock source. The receiver logic is

clocked by the recovered clock from the clock recovery unit, rx_clkout.

This recovered clock is also fed into the FPGA so that, in a multi-crystal

environment, some level of clock domain decoupling can be

implemented to interface with a system clock. On the transmitter channel,

the output of the transmitter PLL, coreclk_out, is sent into the logic

array and also loops back to clock the write side of the transmit phase

compensation FIFO module.

The train receiver PLL CRU clock from the transmitter PLL feature can be

disabled in the altgxb MegaWizard

Plug-In. Deselecting this option

enables an additional rx_cruclk input reference clock port for the

receiver PLL. This feature supports additional multiplication factors for

the receiver PLL and allows for the separation of receiver and transmitter

reference clocks. This separation is required if the output reference clock

frequency from the transmitter PLL exceeds the 325 MHz phase