Altera Stratix GX Transceiver User Manual

Page 302

B–6

Altera Corporation

Stratix GX Transceiver User Guide

January 2005

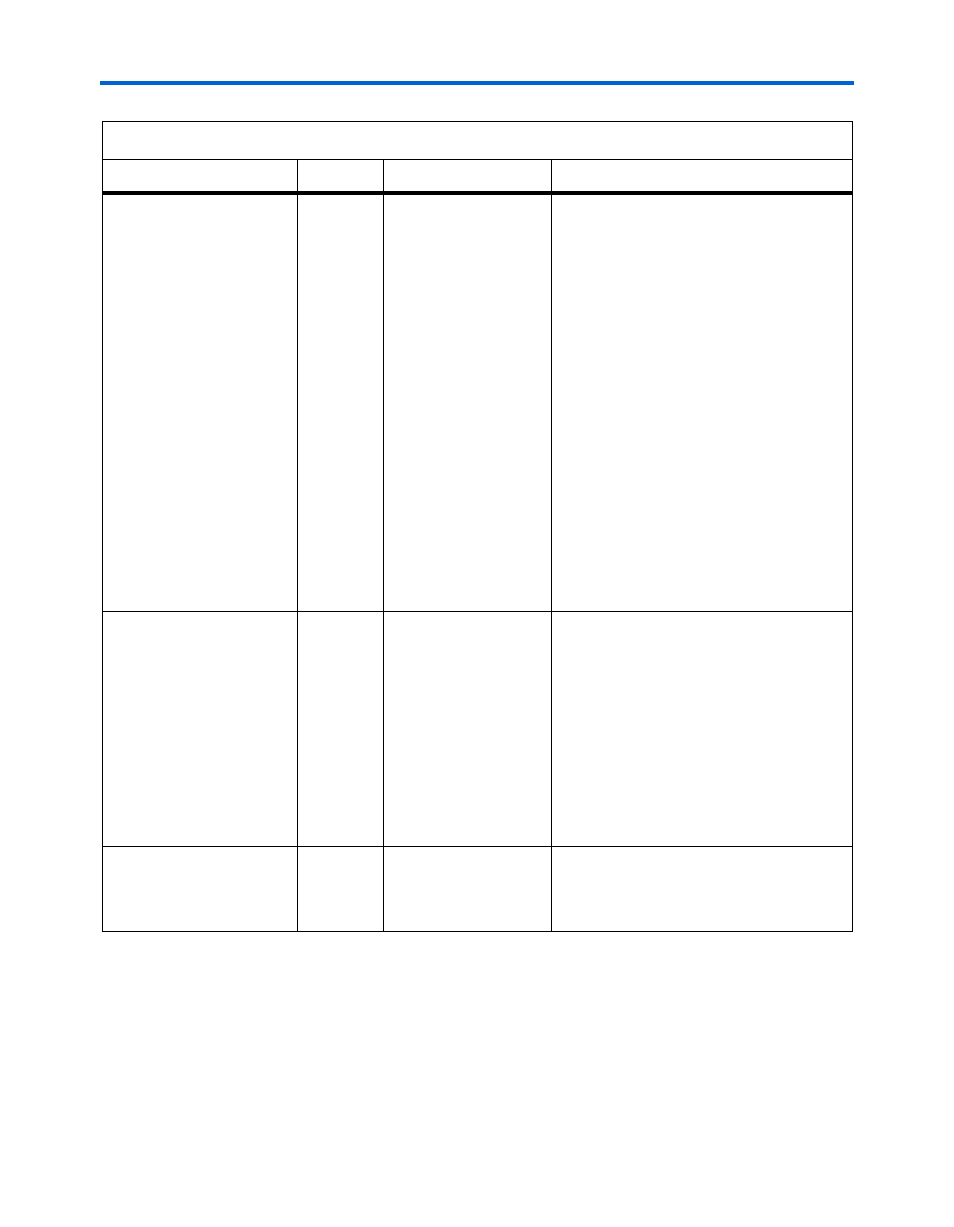

Output Ports

rx_clkout[]

No

Output clock from the

transceiver block

receiver channel.

Output port [NUMBER_OF_CHANNELS -

1..0] wide. If you set the

USE_RATE_MATCH_FIFO

parameter to

ON

and the

CLK_OUT_MODE_REFERENCE

parameter is set to

ON

, the

rx_clkout[]

port is the PLL reference clock with the

period

PLL_INCLOCK_PERIOD

/

DATA_RATE

) *

CHANNEL_WIDTH

. If you

set the

USE_RATE_MATCH_FIFO

parameter to

ON

and the

CLK_OUT_MODE_REFERENCE

parameter

is set to

OFF

, the

rx_clkout[]

port is the

clock output of the PLL. If you set the

USE_RATE_MATCH_FIFO

parameter is

OFF

, the value of the

rx_clkout[]

port

is the same as the value of the

rx_recovclockout[]

port. If you set

the

USE_DOUBLE_DATA_MODE

parameter

OFF

, the clock period must be

doubled, or the clock frequency must be

halved.

rx_locked[]

No

Gives the status of the

transceiver block

receiver channel atom.

Output port [NUMBER_OF_CHANNELS -

1..0] wide. Indicates that the transceiver

block receiver PLL is locked to the

reference input clock (active low). When the

transceiver block receiver PLL is locked,

this signal is GND. When the transceiver

block receiver PLL is out of lock, this signal

is VCC. The signal achieves lock status

within several clock cycles in simulation.

This does not necessarily reflect the real

lock time in hardware, which can take

thousands of cycles for some settings.

rx_channelaligned[]

Yes

Channel alignment

status for the

transceiver block

receiver channels.

Output port [NUMBER_OF_QUADS - 1..0]

wide. If the

PROTOCOL

parameter is set to

XAUI

, the

rx_channelaligned[]

port

must be connected.

Table B–2. Output Ports (Part 2 of 4)

Port Name

Required

Description

Comments