Altera Stratix GX Transceiver User Manual

Page 139

Altera Corporation

5–27

January 2005

Stratix GX Transceiver User Guide

XAUI Mode

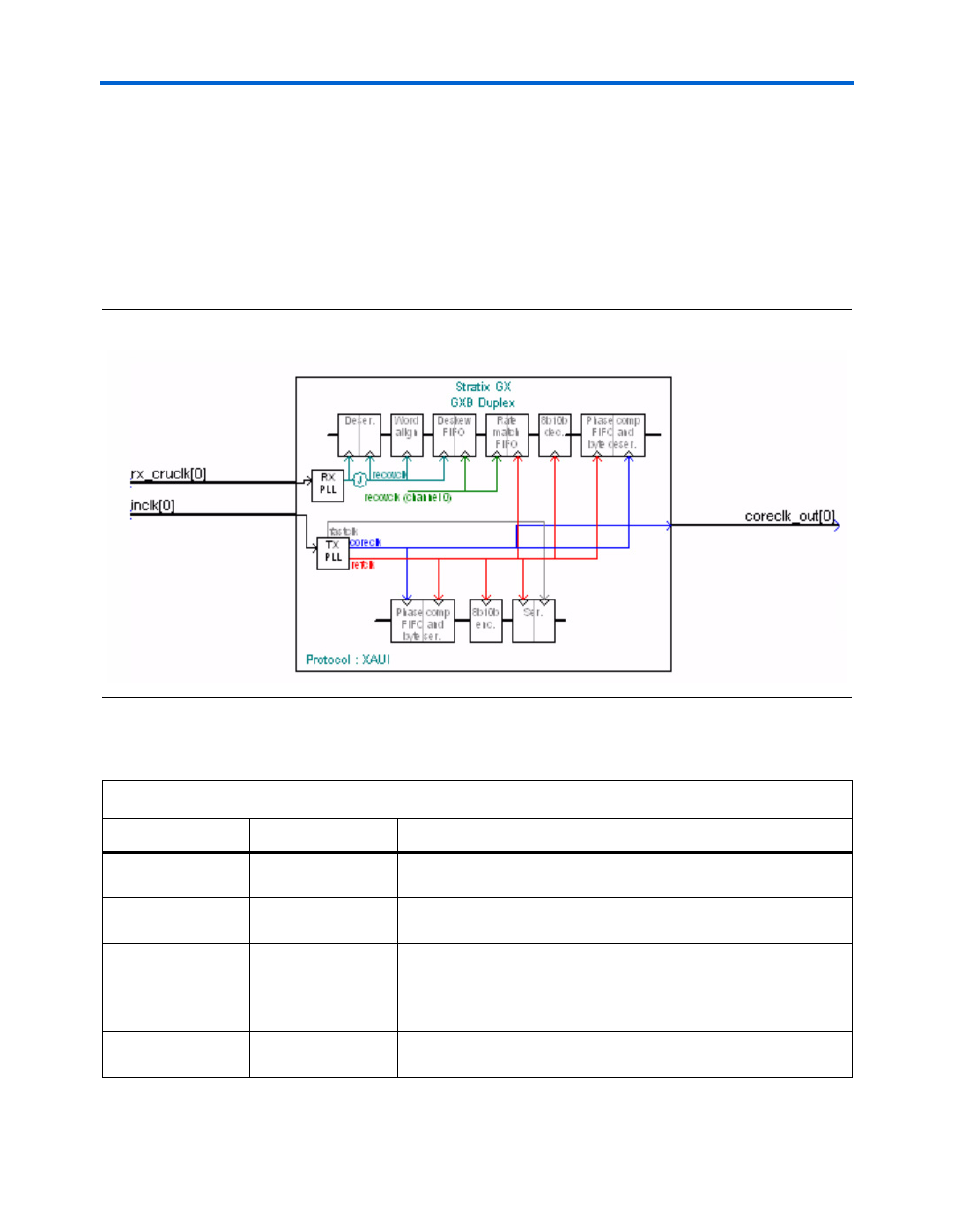

The tx_coreclk must be frequency matched with its respective read

ports. The phase compensation FIFO module can only correct for phase,

not for frequency differences. The receiver parallel interface clocks the

data to the FPGA based on coreclk_out, which is the default option in

the MegaWizard Plug-In Manager.

shows the clock configuration with these optional input ports

enabled.

Figure 5–23. TX_CORECLK Enabled With RX_CRUCLK Port

describes the input and output ports shown in

.

Table 5–5. List of Input & Output Ports Available in XAUI Mode

Clock

Port

Description

inclk

Input

Input to the transmitter PLL. Available as a port when the

transmitter PLL is instantiated.

rx_cruclk

Input

Input to CRU. Available as a port when CRU is not trained by the

transmitter PLL.

tx_coreclk

Input

Clocks write port of the transmitter phase compensation FIFO

module. Optional port in the Quartus

®

II software. Must be

frequency matched to

tx_pll_clk

. If not available as a port, is

fed by

coreclk_out

through logic array routing.

coreclk_out

Output

Output clock from the transmitter PLL equivalent to

tx_pll_clk

.

Available as port if the transmitter PLL is used.