Altera Stratix GX Transceiver User Manual

Page 181

Altera Corporation

6–27

January 2005

Stratix GX Transceiver User Guide

GigE Mode

When determining the location of REFCLKB pins, consider what can be

fed by the pin you choose.

shows the available IQ lines and

which transceiver block REFCLKB drives the REFCLKB pin. This data is

based on the number of transceiver channels in the Stratix GX device.

shows the transceiver routing with respect to inter-

transceiver lines for the EP1SGX25F device. Be sure to use this

information when placing REFCLKB pins. (When placing refclkb pins,

see

Appendix C, REFCLKB Pin Constraints

for information about analog

reads and refclkb pin usage constraints.) For example, if a REFCLKB

pin is required to feed a transmitter PLL using an inter-transceiver line,

the REFCLKB pin cannot be in transceiver block 1, because IQ2 only feeds

the receiver PLLs.

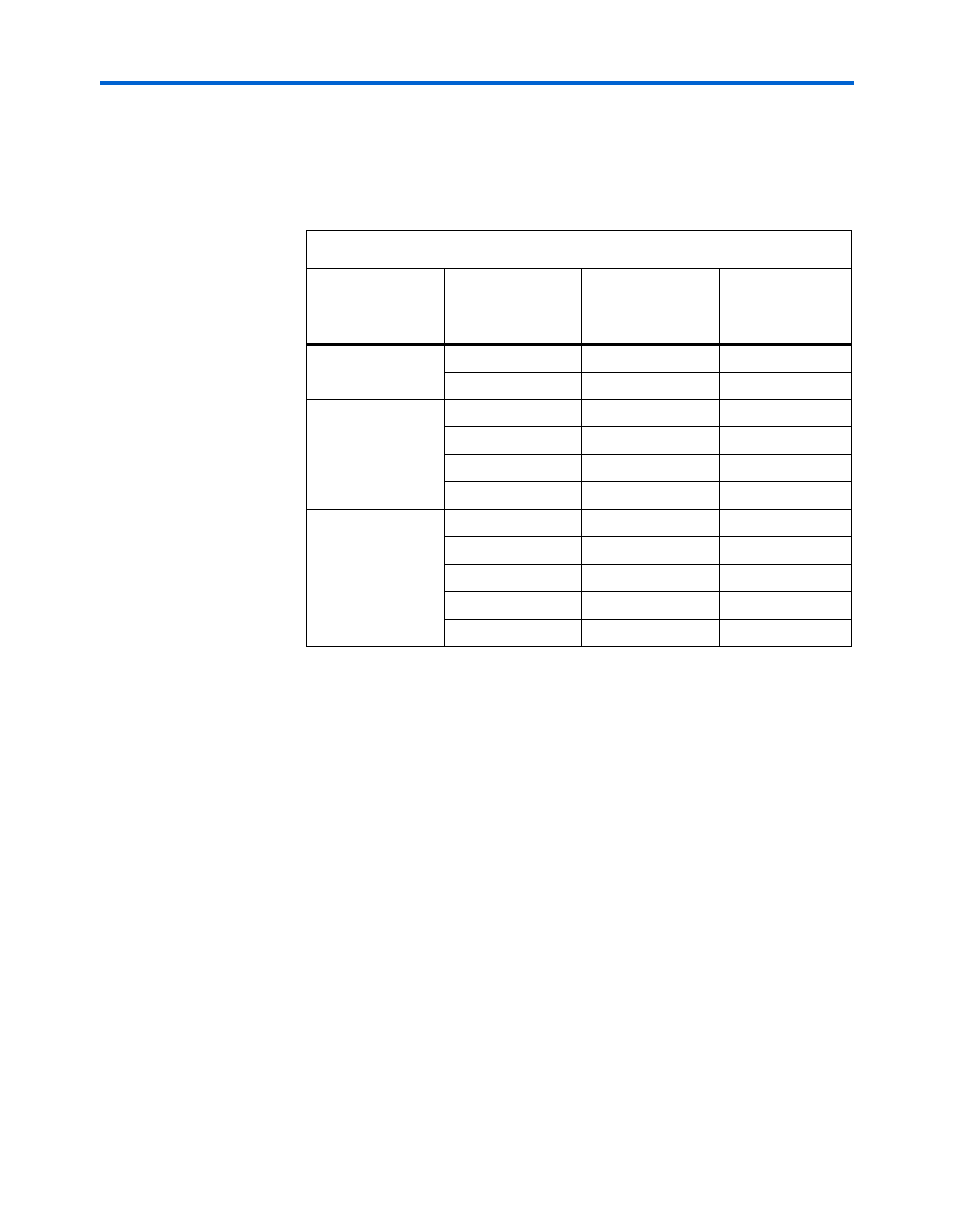

Table 6–3. REFCLKB Pin to Inter-Transceiver Line Connections

Channel Density

REFCLKB Pin in

Transceiver Block

Number

Channels in

Transceiver Block

Inter-Transceiver

Line Driven by

REFCLKB

8 channels

(EP1SGX10)

0

[3:0]

IQ2

1

[7:4]

IQ0

16 channels

(EP1SGX25)

0

[3:0]

—

1

[7:4]

IQ2

2

[11:8]

IQ0

3

[15:12]

IQ1

20 channels

(EP1SGX40)

0

[3:0]

—

1

[7:4]

IQ2

2

[11:8]

IQ0

3

[15:12]

IQ1

4

[19:16]

—