Altgxb instantiation (high_freq_bist.v) – Altera Stratix GX Transceiver User Manual

Page 220

8–16

Altera Corporation

Stratix GX Transceiver User Guide

January 2005

Design Examples

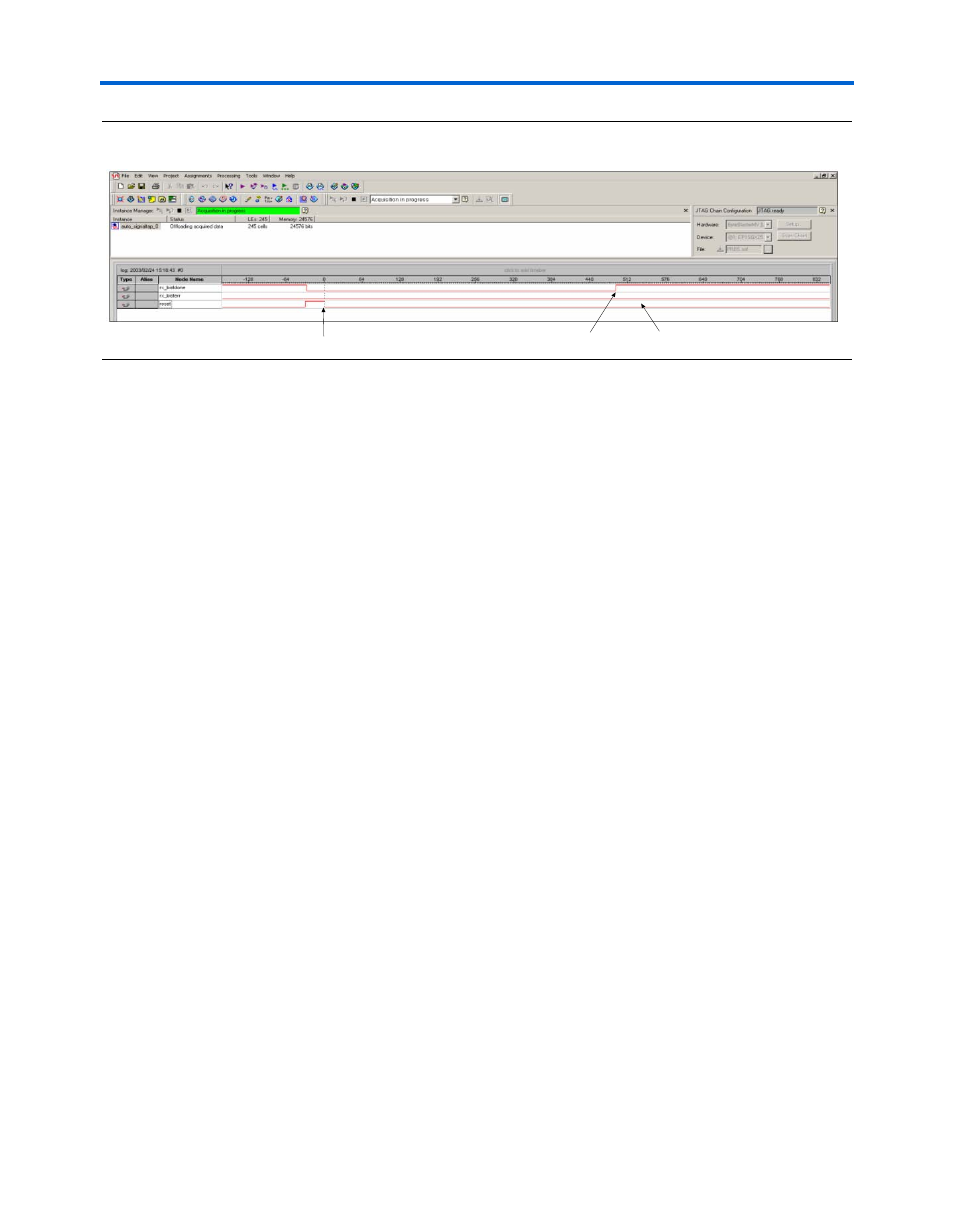

Figure 8–6. SignalTap II Results for PRBS BIST Test Design (Resets the Verifier)

Design 3: High-Frequency Transmitter Generator Design

This design shows how to instantiate the altgxb megafunction in the

high-frequency BIST mode. Because this design consists only of a single

transmitter design, only the altgxb instantiation is shown. The top level

simply consists of calling the megafunction instance.

altgxb Instantiation (High_Freq_BIST.v)

module high_freq_BIST (

inclk,

tx_out,

coreclk_out);

input

[

0:0] inclk;

output [0:0] tx_out;

output [0:0] coreclk_out;

wire [0:0] sub_wire0;

wire [0:0] sub_wire1;

wire [0:0] tx_out = sub_wire0[0:0];

wire [0:0] coreclk_out = sub_wire1[0:0];

altgxb

altgxb_component

(

.inclk (inclk),

.tx_out (sub_wire0),

.coreclk_out (sub_wire1));

defparam

altgxb_component.force_disparity_mode = "OFF",

altgxb_component.channel_width = 16,

(1)

(2)

(3)

resets the verifier

rx_bistdone signifies that the

verification cycle is complete

rx_bisterr remains low,

signifying no bit errors