Basic mode inter-transceiver block clocking – Altera Stratix GX Transceiver User Manual

Page 70

3–24

Altera Corporation

Stratix GX Transceiver User Guide

January 2005

Basic Mode Clocking

Basic Mode Inter-Transceiver Block Clocking

This section describes guidelines for using transceiver interface clocking

between the device logic array and transceiver channels when multiple

transceiver blocks are active. Depending on the mode supported by the

Stratix GX devices, each transceiver block has a different transceiver-to-

device-interface clocking. Different input and output clocks are available

based on the options provided by the MegaWizard Plug-In Manager’s

built-in functions. Support for the number of channels offered varies

depending on which Stratix GX device is selected. Because of the various

configurations of input and output clocks, you must carefully consider

the clocking schemes between transceiver blocks to prevent pitfalls later

in the design cycle.

One of the clocking interfaces to consider while designing with Stratix GX

devices is the transceiver-to-FPGA interface. This clocking scheme is

further classified as the FPGA to transmitter channel and the receiver

channel to the FPGA.

In basic mode, the read port of the transmitter phase compensation FIFO

module is either clocked by the CORECLK_OUT or the TX_CORECLK

signal. The constraint on using TX_CORECLK is that the clock must be

frequency locked to the read clock of the transmitter phase compensation

FIFO module. Synchronous data transfers for a multi-transceiver block

configuration can be accomplished by using the TX_CORECLK port. The

TX_CORECLK

of multi-transceiver blocks is connected to a common clock

domain either from a single CORECLK_OUT signal or from a device

system clock domain. This scheme is shown in

.

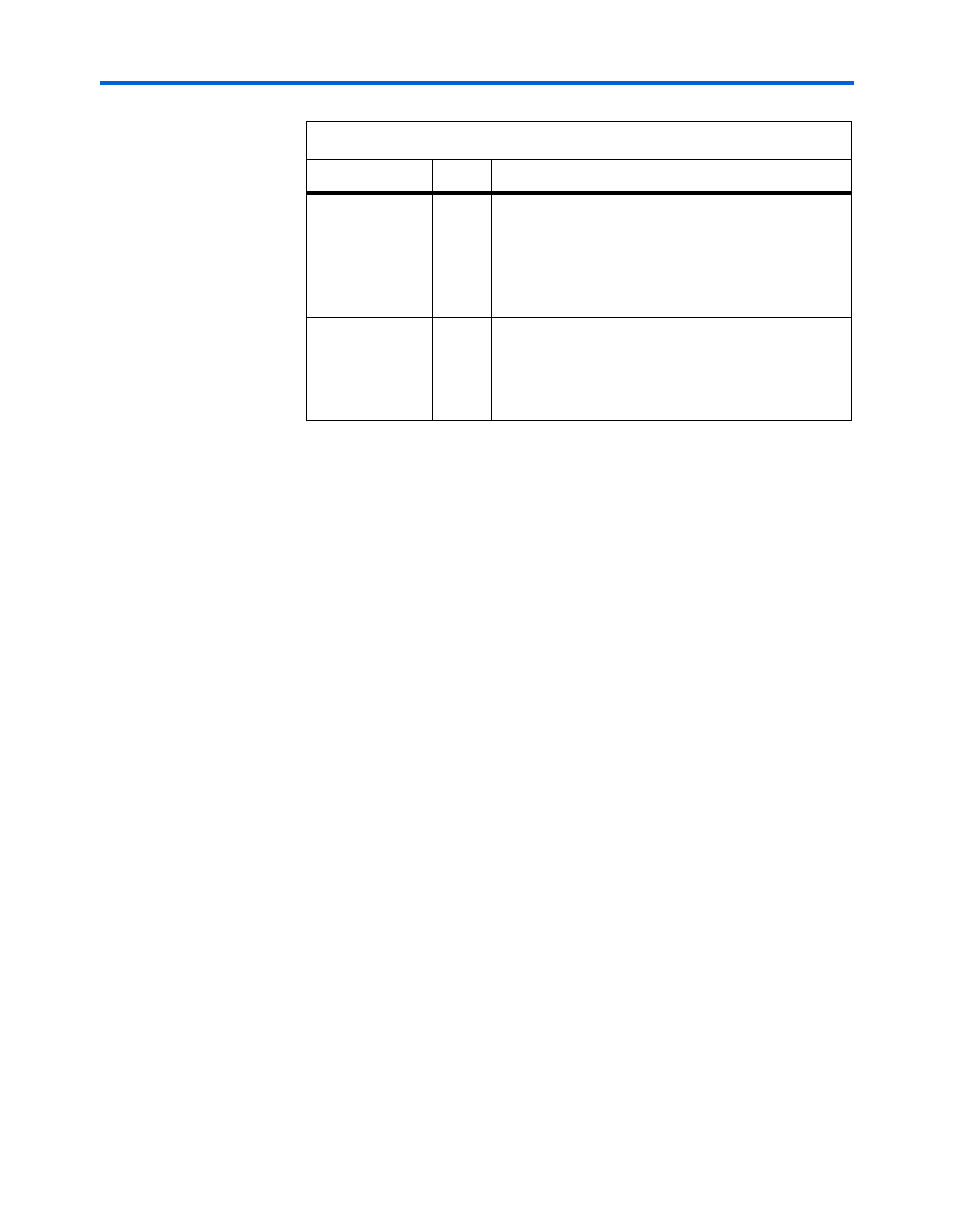

tx_coreclk

Input

Clocks write port of transmitter phase compensation

FIFO module. Available as optional port in the

Quartus II MegaWizard

®

Plug-In Manager. Must be

frequency matched to

TX_PLL_CLK

. If not available

as a port, this is fed by

CORECLK_OUT

through logic

array routing.

rx_coreclk

Input

Clocks read port of Receiver phase compensation

FIFO module. Available as optional port in the

Quartus II MegaWizard Plug-In Manager. If not

available as a port, this is fed by

RX_CLKOUT

through logic array routing.

Table 3–3. Input & Output Ports Available in Basic Mode (Part 2 of 2)

Clock

Port

Description