Table 9–1 – Altera Stratix GX Transceiver User Manual

Page 229

Altera Corporation

9–3

January 2005

Stratix GX Transceiver User Guide

Reset Control & Power Down

In 16-bit or 20-bit mode, asserting rxdigitalreset causes the

recovered clock or the slow clock to reset. The slow clock is divided down

by the deserialization factor from rx_clkout. Altera recommends

synchronizing rxdigitalreset to the FPGA or the logic array clock.

Link initialization must be performed after any reset condition. You must

determine when the data is valid after reset (for example, by using the

rx_syncstatus

signal in XAUI mode).

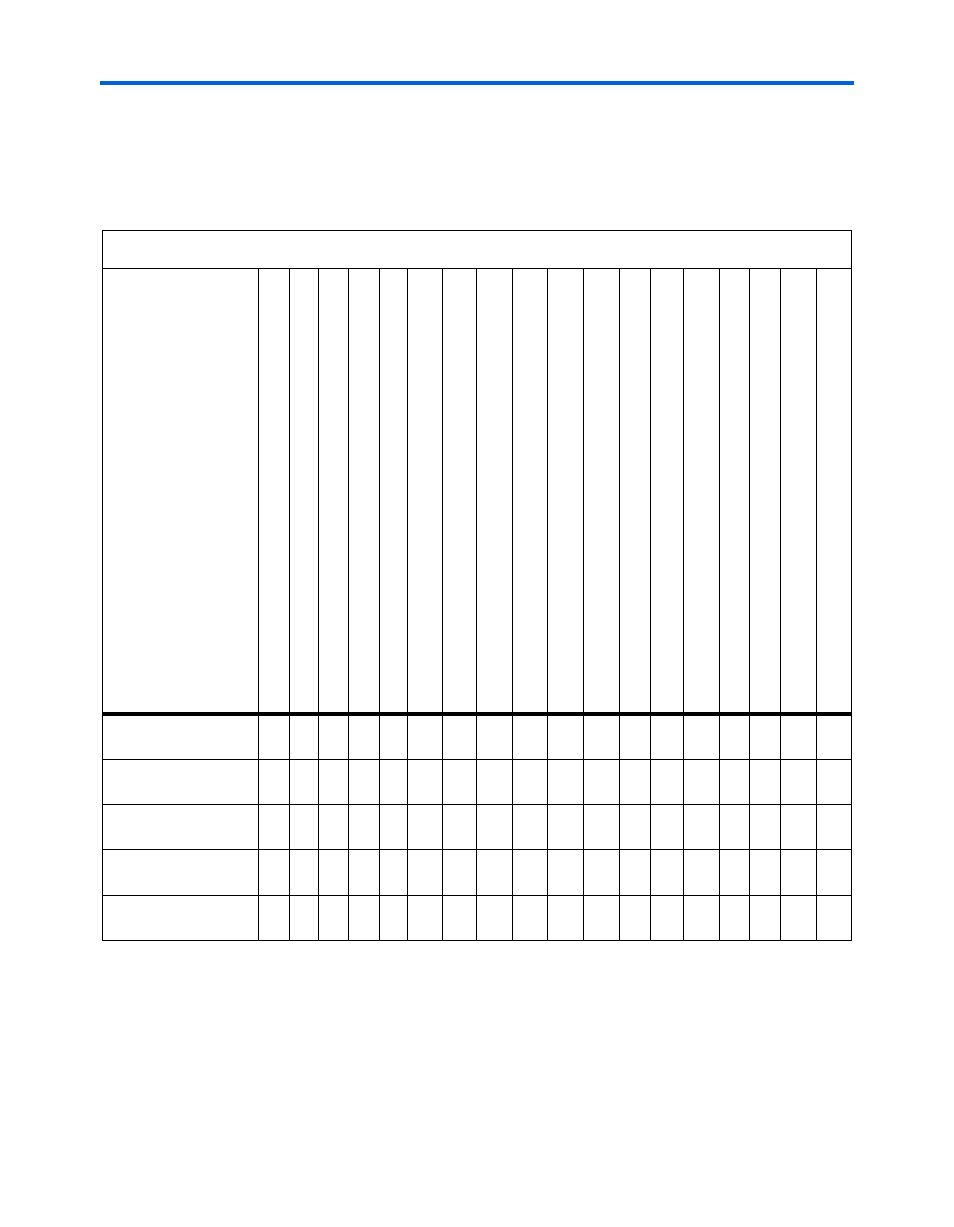

Table 9–1. Reset Signal Map to Stratix GX Blocks

Tr

ansmitter Ph

ase Compensation

F

IFO

Module/ Byte Serializer

Tr

ansmitter 8B/10B

En

coder

Tr

ansmitter Ser

ialize

r

Tr

ansmitter

Analog

Circuits

Tr

ansmitter PLL

Tr

ansmitter XAUI State Machine

Tr

ansmitter

Analog

Circuits

BIST Gener

ators

Rece

iver

Deserializer

Receiver W

o

rd Aligne

r

Re

ceiver Deskew

FIFO Module

Receiver Rate

Matcher

Re

ceiver 8B/10B

Deco

der

Receiver Phase Compensa

tion

FI

F

O

Module/ Byte De

serializer

Receiver

PLL / CRU

Receiver XAUI State Machine

BIST V

e

rifiers

Receiver Analog Circuits

rxdigitalreset

v v v v v

v v

rxanalogreset

v

v

v

txdigitalreset

v v

v

v

pll_areset

v v v v v v v v v v v v v v v v v v

pllenable

v v v v v v v v v v v v v v v v v v