Altera Stratix GX Transceiver User Manual

Page 303

Altera Corporation

B–7

January 2005

Stratix GX Transceiver User Guide

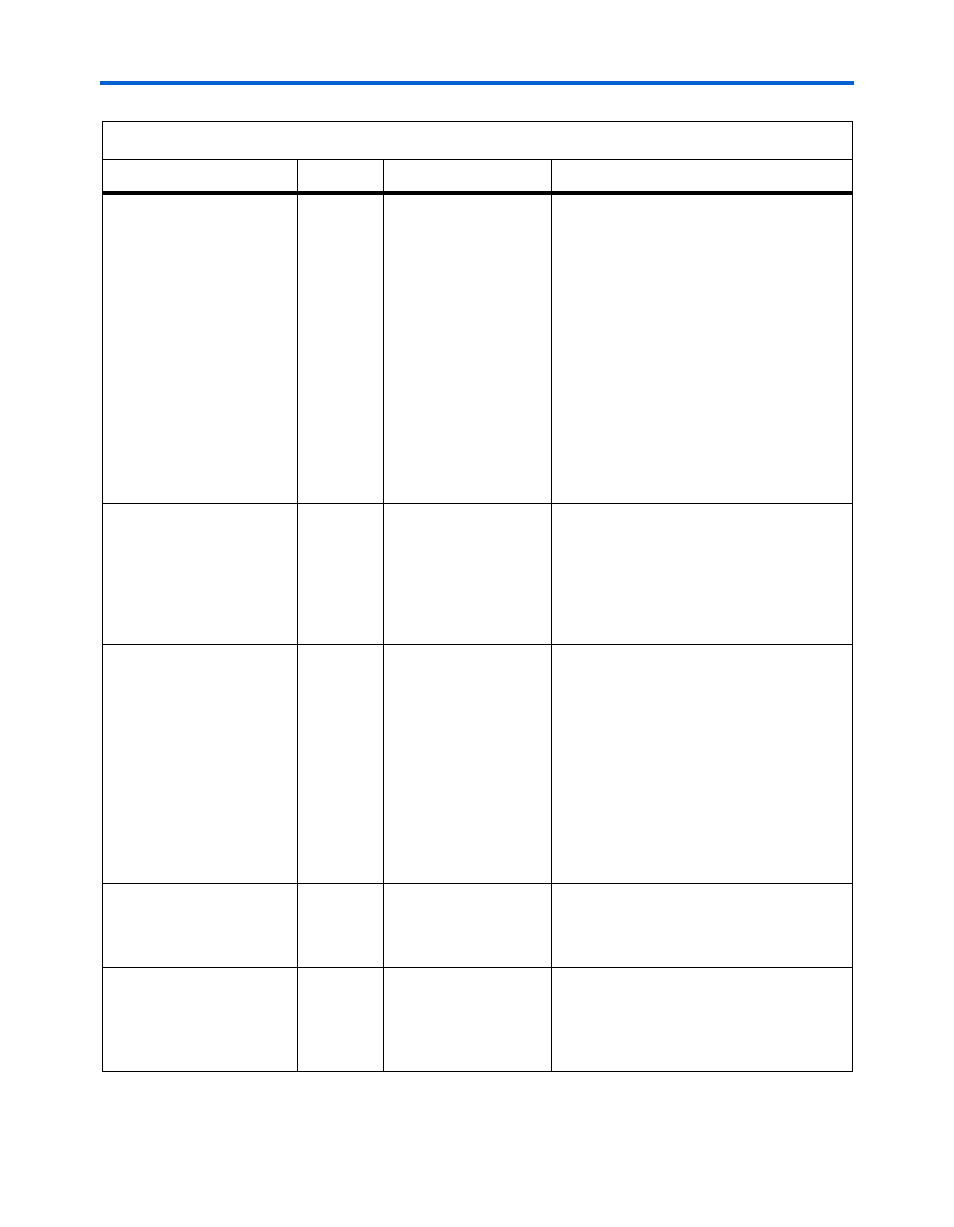

rx_freqlocked[]

No

Indicates whether

transceiver block

receiver channel is

locked to the data mode

in the

rx_in[]

port.

Output port [NUMBER_OF_CHANNELS -

1..0] wide. This port is asserted when the

GXB receiver PLL moves to lock to the

received data mode. At that time, the clock

recovery unit (CRU) for the GXB receiver

PLL is frequency and phase-locked to the

reference clock and starts using the phase

detector to lock onto the incoming data, but

it is not yet locked to the data. It takes a

finite time before the CRU for the GXB

receiver PLL is locked onto the data. The

signal achieves lock status within several

clock cycles in simulation. This does not

necessarily reflect the real lock time in

hardware, which can take thousands of

cycles for some settings.

rx_rlv[]

No

Indicates whether the

transceiver block

receiver channel

violated the value

specified for the

RUN_LENGTH

parameter.

Output port [NUMBER_OF_CHANNELS -

1..0] wide.

rx_syncstatus[]

No

Provides the status of

the pattern detector

and word aligner.

Output port [NUMBER_OF_CHANNELS *

DWIDTH_FACTOR - 1..0] wide. If you set

the

PROTOCOL

parameter to

XAUI

or

GigE

, the

rx_syncstatus[]

port is

connected to the synchronization state

machine and indicates that the channel

completed synchronization. If you set the

PROTOCOL

parameter to anything other

than

XAUI

or

GigE

, the

rx_syncstatus[]

port becomes a

resync signal for manual synchronization of

the alignment system.

rx_patterndetect[]

No

Indicates whether the

pattern detector

detected the

programmed pattern.

Output port [NUMBER_OF_CHANNELS *

DWIDTH_FACTOR - 1..0] wide.

rx_ctrldetect[]

No

Indicates whether the

8B/10B decoder

detects a control code.

Output port [NUMBER_OF_CHANNELS *

DWIDTH_FACTOR - 1..0] wide. If you set

the

USE_8B_10B_MODE

parameter to

OFF

, the

rx_ctrldetect

port is not

available.

Table B–2. Output Ports (Part 3 of 4)

Port Name

Required

Description

Comments