Altera Stratix GX Transceiver User Manual

Page 271

Altera Corporation

9–45

January 2005

Stratix GX Transceiver User Guide

Reset Control & Power Down

The difference in this configuration from the configuration in

CRU With Transmit PLL Output Clock Option Enabled” on page 9–32

is

that receive CRU is trained by the input pin rx_cruclk.

shows the receive-only configuration with clock options

disabled.

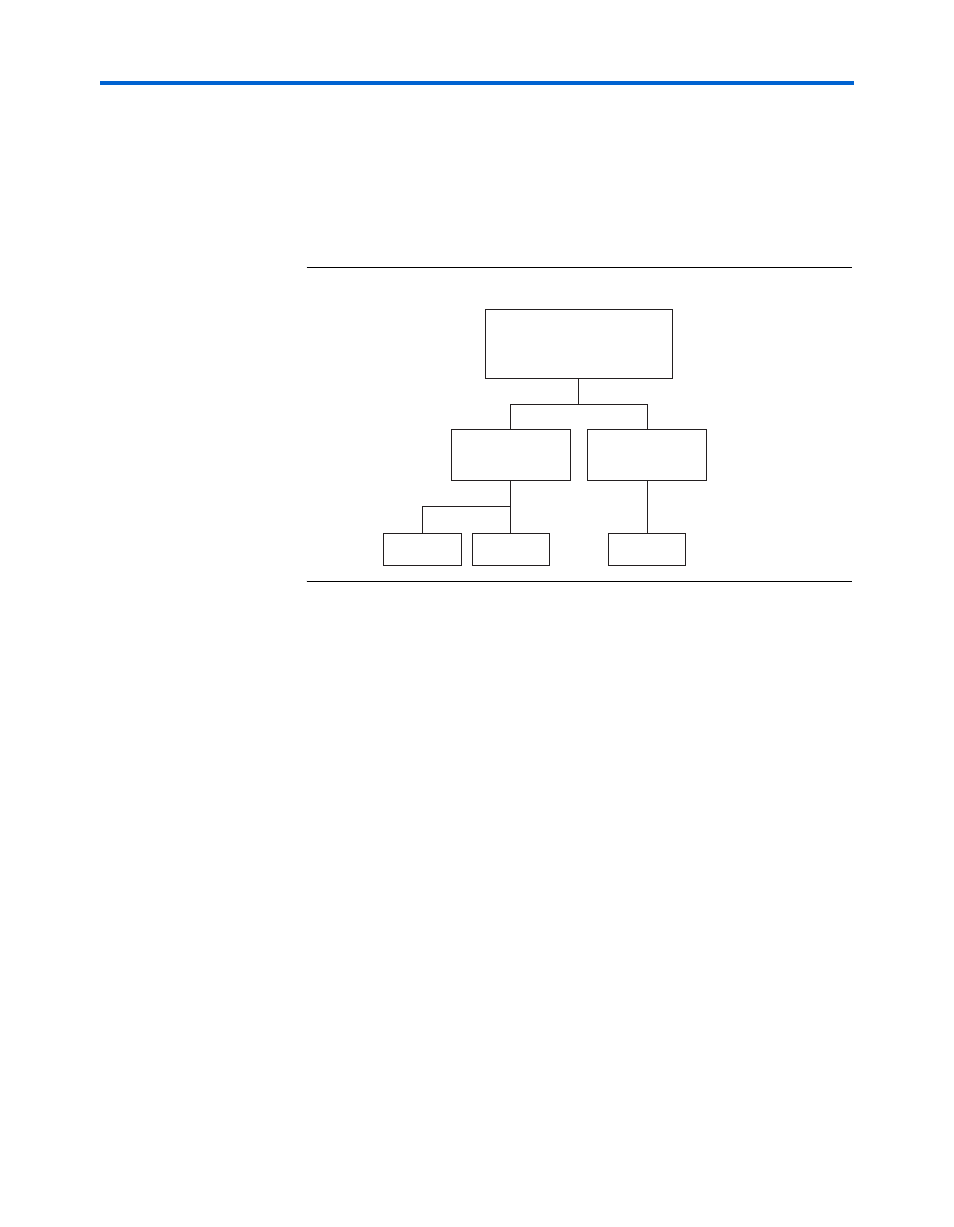

Figure 9–13. Receive Clock Only With Clock Options Disabled

Design Example 1

This design example shows a receive only configuration with

rx_cruclk

as the receive CRU input reference clock and rx_coreclk

as the receive parallel interface clock.

This design example has the following constraints:

■

If your design requirements are different from the examples, use the

flow charts and waveforms for each configuration as design

guidelines.

■

The design example requires a reset controller that generates a

sync_reset

(synchronous reset) for the entire system.

■

The design example has an async_reset (a power down in GXB

terms) and digital resets for transmit and receive. All user input

digital resets must be at least four cycles long.

■

This design example does not cover all the digital reset scenarios in

a system that resets the digital logic of the GXB.

■

In this example, whenever the rx_freqlocked signal toggles the

rxdigitalreset

, the receiver’s digital circuit is reset. However,

you can make changes to the design to avoid this if, for example, you

want to debug your design without the core being reset.

Receive Only with Train RX

CRU with TXPLL Output Clock

Option Disabled

Single Width

(8/10)

Double Width

(16/20)

rx_clkout

rx_coreclk

rx_clkout

Receive Parallel Clock

data path width

Receive Parallel Clock