Parallel loopback, Parallel loopback –2, Ii software or on the user setting – Altera Stratix GX Transceiver User Manual

Page 202

7–2

Altera Corporation

Stratix GX Transceiver User Guide

January 2005

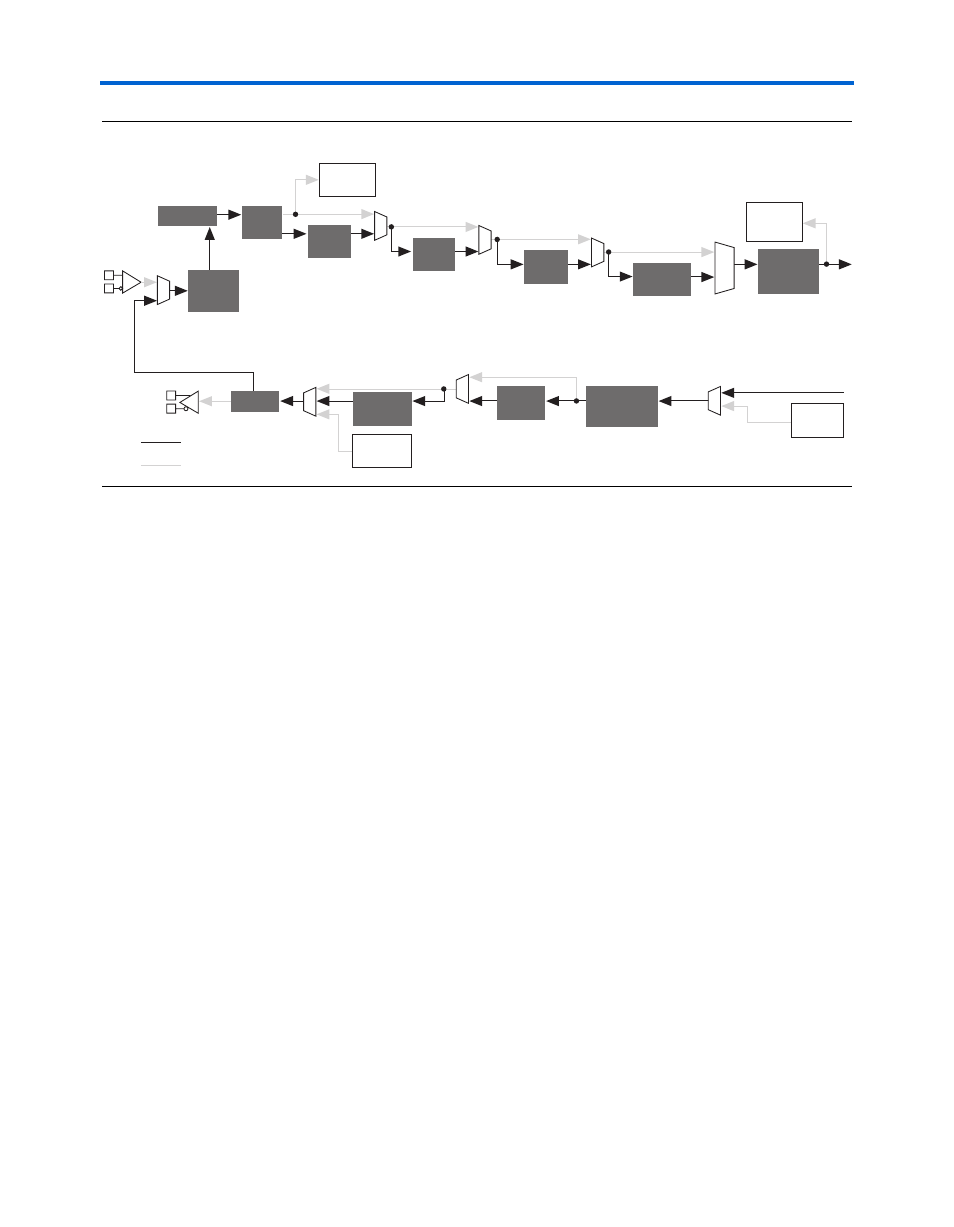

Parallel Loopback

Figure 7–1. Stratix GX Block in Serial Loopback Mode

Parallel

Loopback

shows the data path for parallel loopback. A data stream is fed

to the transmitter from the FPGA logic array and has the option of using

blocks in the transmitter block. The data then exits the transmitter into the

receiver in parallel form before entering the serializer. The data enters the

receiver block after the deserializer and has the option of using any of the

subsequent receiver blocks before being output by the receiver into the

FPGA logic array. The PRBS block generates data. When using parallel

loopback, the tx_out ports are active, and the differential output voltage

on the tx_out ports is based on the current setting in the Quartus

®

II

software or on the user setting.

Non-Active Path

Active Path

Clock

Recovery

Unit

BIST PRBS

Verifier

BIST

Incremental

Verifier

Channel

Aligner

Rate

Matcher

8B/10B

Decoder

Byte

Deserializer

Phase

Compensation

FIFO

Byte

Serializer

Serializer

BIST PRBS

Generator

8B/10B

Encoder

Deserializer

Word

Aligner

Phase

Compensation

FIFO

BIST

Generator