Byte serializer, 8b/10b encoder – Altera Stratix GX Transceiver User Manual

Page 63

Altera Corporation

3–17

January 2005

Stratix GX Transceiver User Guide

Basic Mode

If the TX_CORECLK is not selected as an optional input transmitter port,

TX_CORECLK

is fed by CORECLK_OUT. This connection occurs using the

logic array routing. In this situation, the software defaults to using an

FPGA global clock, a regional clock, or a fast regional clock resource.

The transmitter phase compensation FIFO buffer is always used and

cannot be bypassed. The input to the transmitter phase compensation

FIFO module is the data from the device logic array. If they are used, the

tx_ctrlenable

and tx_forcedisparity signals are also passed

through the FIFO module to ensure that they are synchronized with the

data when they feed the 8B/10B encoder module.

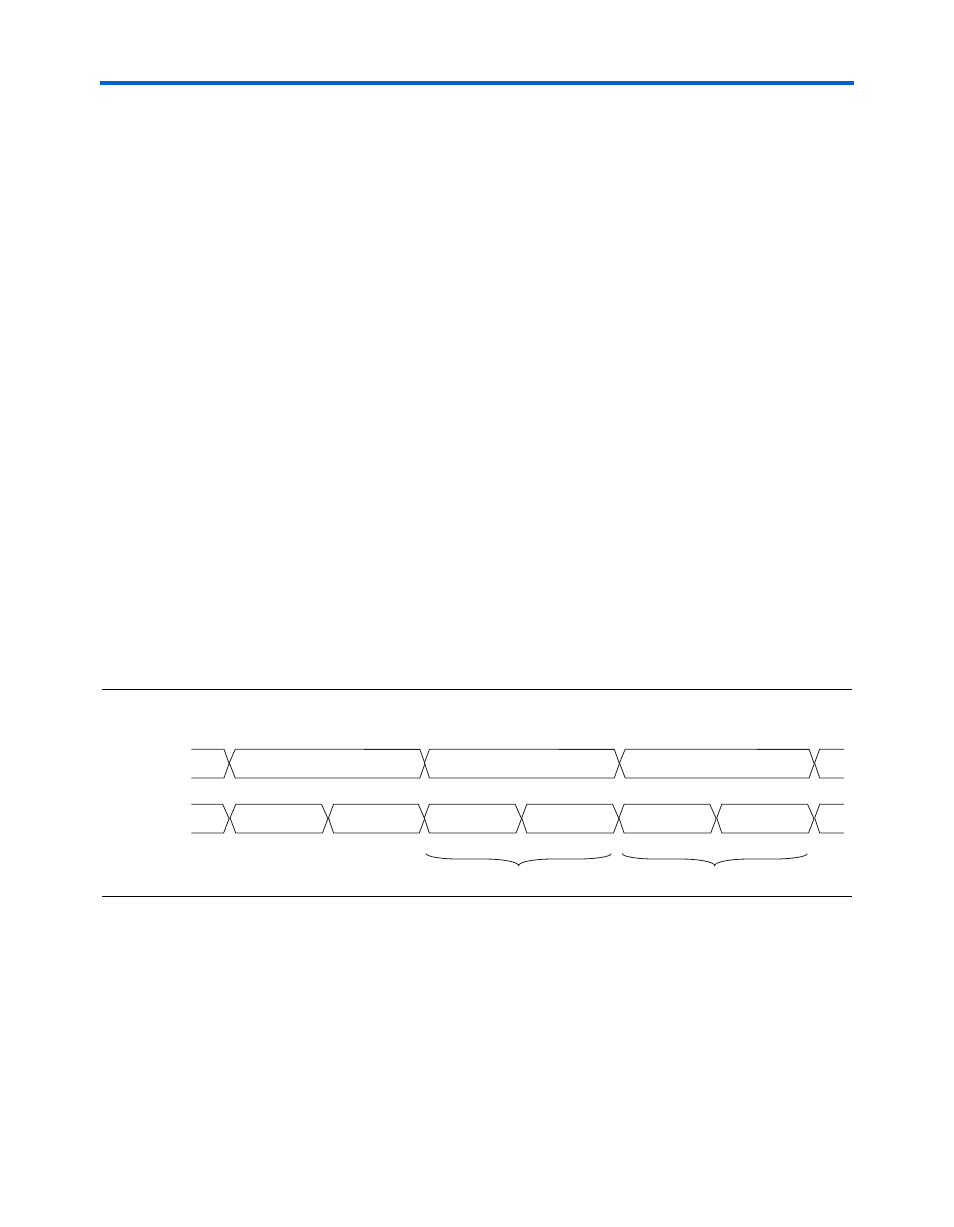

Byte Serializer

The byte serializer in the transmitter block takes in a 20- or 16-bit input

from the phase compensation FIFO module and serializes it to 10 or 8 bits.

It transmits the least significant byte to the most significant byte. Altera

®

recommends using the transmitter digital reset to reset the byte serializer

FIFO module pointers whenever an unknown state is encountered: for

example, periods when the transmitter PLL unlocks. Refer to the Reset

Control & Power Down chapter for further details on the reset sequence.

demonstrates input and output signals of the byte serializer

when serializing a 20-bit input to 10 bits. The tx_in[] signal is the input

from the FPGA logic array that has already passed through the

transmitter phase compensation FIFO buffer.

Figure 3–15. Transmitter Byte Serializer in 20- to 10-Bit Mode

The LSB is transmitted before the MSB in the Transmitter byte serializer.

For the input of D1, the output is D1LSB and then D1MSB.

8B/10B Encoder

The 8B/10B encoder is part of the Stratix GX transceiver block. The

purpose of the 8B/10B encoder is to translate 8-bit data and a 1-bit control

identifier (via tx_ctrlenable) into a 10-bit DC-balanced data stream.

datain[19..0]

dataout[9..0]

D1

D2

D3

11111000001010100000

xxxxxxxxxx

1010100000

xxxxxxxxxx

1111100000

1100011000

1111000111

11000110001111000111

10101010101100110011

MSB

LSB

D1

LSB

MSB

D2