Altera Stratix GX Transceiver User Manual

Page 232

9–6

Altera Corporation

Stratix GX Transceiver User Guide

January 2005

Recommended Resets

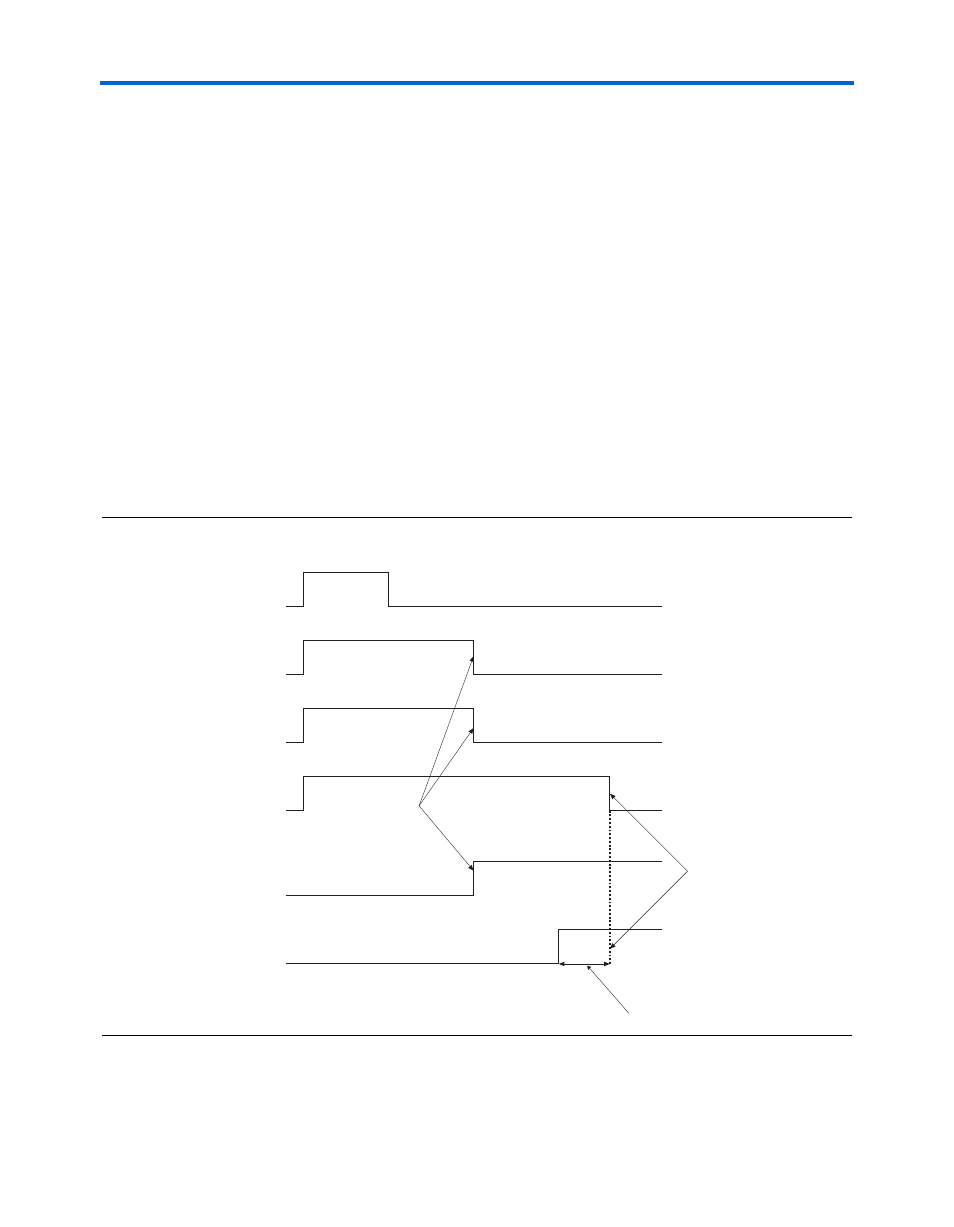

The waveform in

shows the functionality of the receiver and

transmitter reset sequence shown in

. The pll_areset signal

resets the entire transceiver block, including both the analog and digital

portions of the transmitter and receiver (see

). After the

pll_areset

signal goes low, the controller waits until the transmitter

PLL is stable (pll_locked = 1’b1) before sending the tx_digitalreset

and rx_analogreset low. This ensures that the output of the

transmitter PLL is stable before releasing any of the logic that it feeds. The

transmitter PLL clock in this case also trains the receiver PLL. After the

CRU has transitioned to locking to data from locking to the reference

clock, the rx_freqlocked signal goes high, which allows the CRU to

transition into the wait state where a timer is loaded a certain amount of

time. See the Stratix GX FPGA Family data sheet for the amount of time

loaded into the timer. When the timer counts down, rx_clkout is stable.

The reset controller then sends rx_digital low, completing the reset

sequence. You will be able to monitor the BER (for example, a

synchronization state machine based on the Stratix GX transceiver data)

to determine whether the system is initialized and working properly.

Figure 9–4. Receiver & Transmitter Reset Sequence Waveforms

pll_areset

tx_digitalreset

rx_analogreset

rx_digitalreset

pll_locked

rx_freqlocked

Output Status Signals

Reset Signals

Stable Recovered Clock

Stable Transmit

Pll Clock

Trx_freqlock2phaselock